# Smart Mobility ARChitecture Design Guide

SMARC Design Guide 2.0 March 23, 2017

© Copyright 2017, SGeT Standardization Group for Embedded Technology e.V.

Note that some content of this SGeT document may be legally protected by patent rights not held by SGeT. SGeT is not obligated to identify the parts of this specification that require licensing or other legitimization. The contents of this SGeT document are advisory only. Users of SGeT documents are responsible for protecting themselves against liability for infringement of patents. All content and information within this document are subject to change without prior notice.

SGeT provides no warranty with regard to this SGeT document or any other information contained herein and hereby expressly disclaims any implied warranties of merchantability or fitness for any particular purpose with regard to any of the foregoing. SGeT assumes no liability for any damages incurred directly or indirectly from any technical or typographical errors or omissions contained herein or for discrepancies between the product and this SGeT document. In no event shall SGeT be liable for any incidental, consequential, special, or exemplary damages, whether based on tort, contract or otherwise, arising out of or in connection with this SGeT document or any other information contained herein or the use thereof.

# **REVISION HISTORY**

| Revision Comments                                                                    |  | Originator           | Date           |

|--------------------------------------------------------------------------------------|--|----------------------|----------------|

| 1.0 Initial Release                                                                  |  | S. Milnor / Kontron  | July 1, 2013   |

| 1.1 Created sharper images for Fig 19, 60, 69 Fixed small typos and grammar mistakes |  | S. Milnor / Kontron  | July 5, 2013   |

| ,                                                                                    |  | B. Mayer / Technagon | March 23, 2017 |

# **CONTENTS**

| 1 |           | on                                                 |    |

|---|-----------|----------------------------------------------------|----|

|   | 1.1 Gene  | eral Introduction                                  | 10 |

|   | 1.2 Purp  | ose of This Document                               | 10 |

|   | 1.3 Desi  | gn Help                                            | 10 |

|   | 1.4 Abbr  | eviations and Acronyms Used                        | 11 |

|   |           | ıment References                                   |    |

|   | 1.5.1     | SGET Documents                                     |    |

|   | 1.5.2     | Industry Standards Documents                       |    |

|   | -         | ematic Example Correctness                         |    |

|   |           | vare Support                                       |    |

|   |           | ematic Example Conventions                         |    |

| 2 |           | ture: Connector, Power Delivery, System Management |    |

| _ |           | ule Connectorule                                   |    |

|   |           | ule Power                                          |    |

|   | 2.2.1     | Input Voltage Range                                |    |

|   | 2.2.1     | Input Voltage Range                                |    |

|   | 2.2.2     | Module Maximum Input Power                         |    |

|   |           |                                                    |    |

|   | 2.2.4     | Power Path                                         |    |

|   |           | ule I/O VoltagePWR BAD#                            |    |

|   |           |                                                    |    |

|   |           | RIER_PWR_ON                                        |    |

|   |           | et In to Module                                    |    |

|   |           | er Button                                          |    |

|   |           | e Recovery                                         |    |

|   |           | er Up Sequence                                     |    |

|   | 2.9.1     | CARRIER_STBY#                                      |    |

|   |           | Selection                                          |    |

|   | 2.10.1    | Boot Definitions                                   |    |

|   | 2.10.2    | SMARC BOOT_SEL Pins                                |    |

|   |           | Backup Power                                       |    |

| ^ |           | erved / Test Interfaces                            |    |

| 3 |           | terfaces                                           |    |

|   |           | ule LVDS                                           |    |

|   |           | NEC 1280 x 768 Single Channel LVDS Example         |    |

|   |           | LVDS Dual Channel example                          |    |

|   |           | Display Parameters and EDID                        |    |

|   |           |                                                    |    |

|   |           | ayPort (DP++)                                      |    |

|   |           | HDMI over DP++                                     |    |

|   |           | edded DisplayPort (eDP)                            |    |

|   |           | DSI                                                |    |

| 4 | Low / Med | dium Speed Serial I/O Interfaces                   | 42 |

|   | •         | chronous Serial Ports                              |    |

|   | 4.1.1     | RS232 Ports                                        |    |

|   |           | RS485 Half-Duplex                                  |    |

|   |           | nterfaces                                          |    |

|   | 4.2.1     | General                                            |    |

|   | 4.2.2     | I2C Level Translation, Isolation and Buffering     |    |

|   | 4.2.3     | I2C_PM Bus EEPROMs                                 |    |

|   | 4.2.4     | General I2C Bus EEPROMs                            |    |

|   | 4.2.5     | I2C Based I/O Expanders                            |    |

|   | 4.2.6     | Other I2C Devices                                  |    |

|   |           | ch Screen Controller Interfaces                    |    |

|   | 4.3.1     | General                                            |    |

|   | 4.3.2     | Interface Types / Driver Considerations            | 53 |

|   | 4.3.3   | Touch Controller Modules / ICs / Screens          |      |

|---|---------|---------------------------------------------------|------|

|   | 4.3.4   | I2C Interface to Touch Controller                 | . 55 |

|   | 4.4 123 | S Interfaces                                      | . 56 |

|   | 4.4.1   | General Information                               |      |

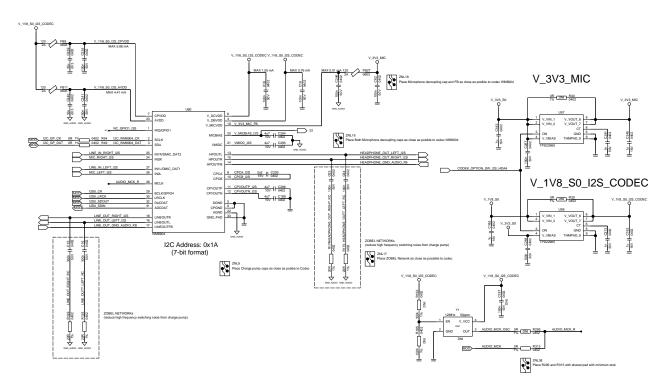

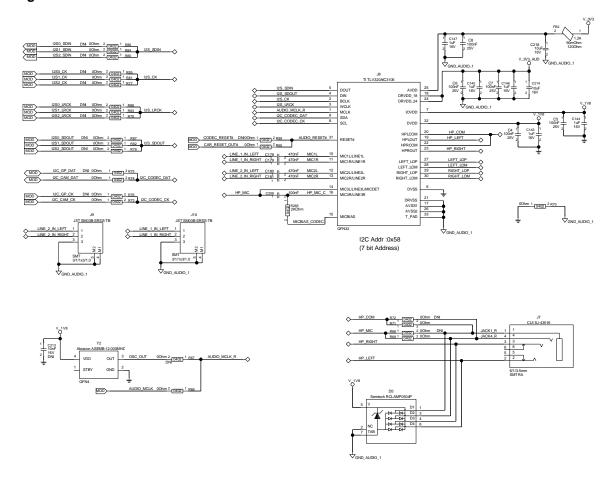

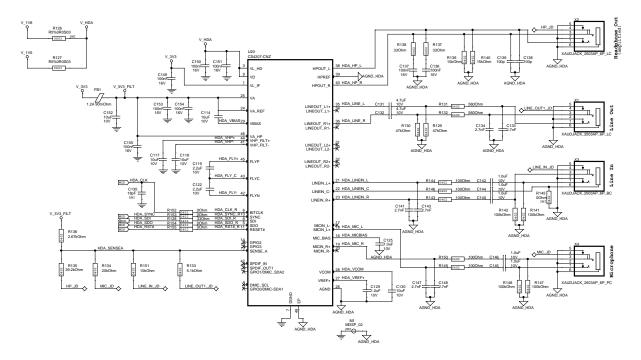

|   | 4.4.2   | Cirrus Logic I2S Audio Example                    |      |

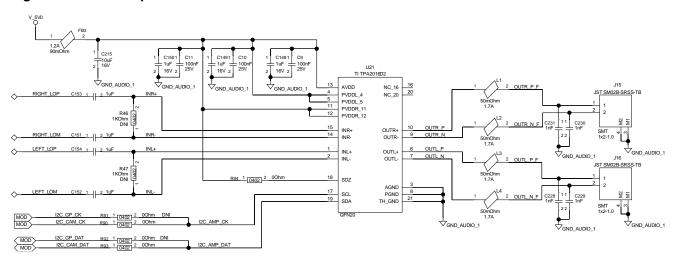

|   | 4.4.3   | Texas Instruments TLV320AIC3105 I2S Audio Example |      |

|   | 4.4.4   | Intel High Definition Audio over I2S2             |      |

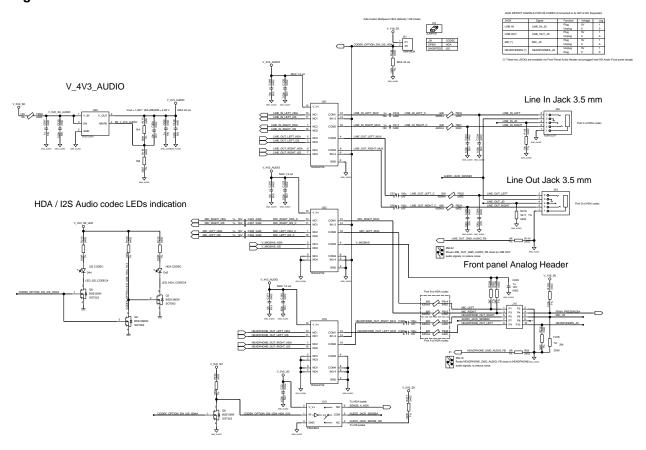

|   | 4.4.6   | Audio Switch                                      |      |

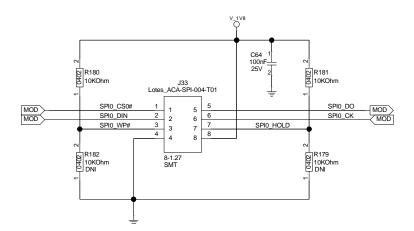

|   |         | Pl Interfaces                                     |      |

|   | 4.5.1   | General                                           |      |

|   | 4.5.2   | SMARC Implementation                              |      |

|   | 4.5.2   | SPI Device Examples – 1.8V I/O                    |      |

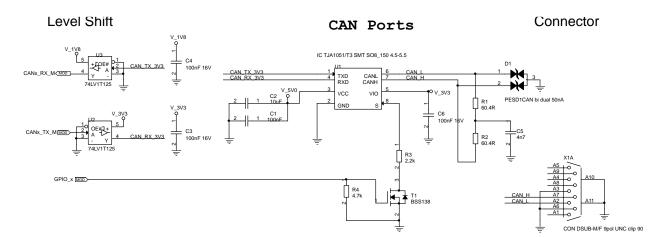

|   |         | AN Bus                                            |      |

|   |         | General                                           |      |

|   | 4.6.1   |                                                   |      |

|   | 4.6.2   | SMARC Implementation                              |      |

| _ | 4.6.3   | Isolation                                         |      |

| ) |         | peed Serial I/O Interfaces                        |      |

|   |         | SB                                                |      |

|   | 5.1.1   | General                                           | _    |

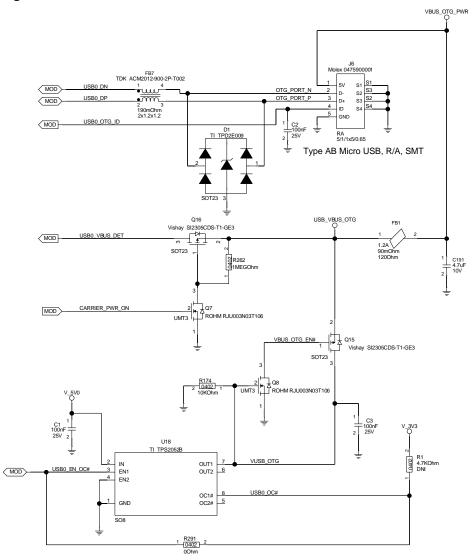

|   | 5.1.2   | USB0 Client / Host Direct From Module             |      |

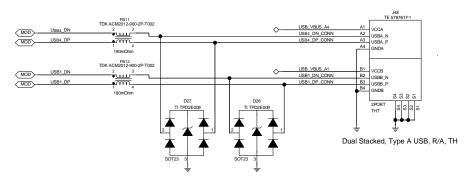

|   | 5.1.3   | USB1 and USB2 Host Ports direct from Module       |      |

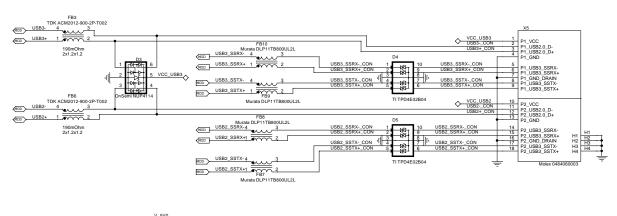

|   | 5.1.4   | USB 3.0                                           | _    |

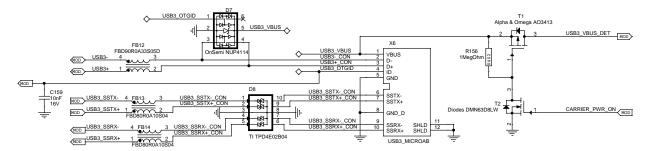

|   | 5.1.5   | USB 3.0 OTG                                       |      |

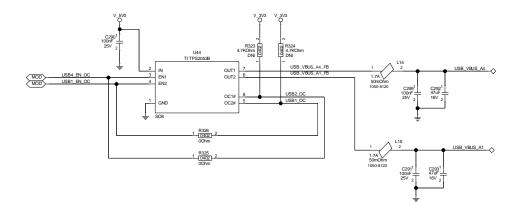

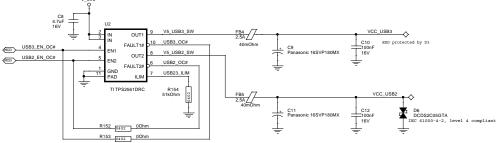

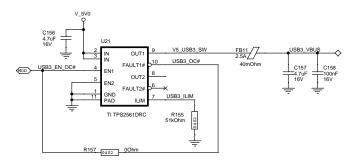

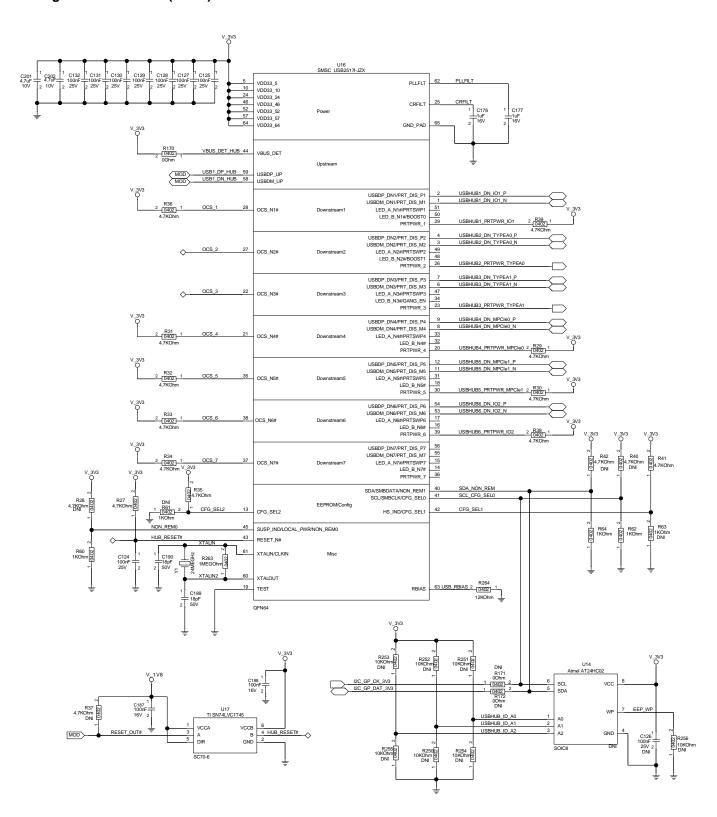

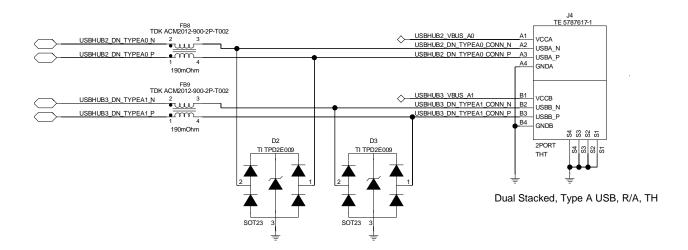

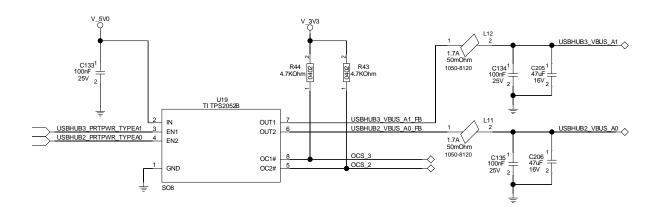

|   | 5.1.6   | USB Hub On Carrier                                |      |

|   |         | BE                                                |      |

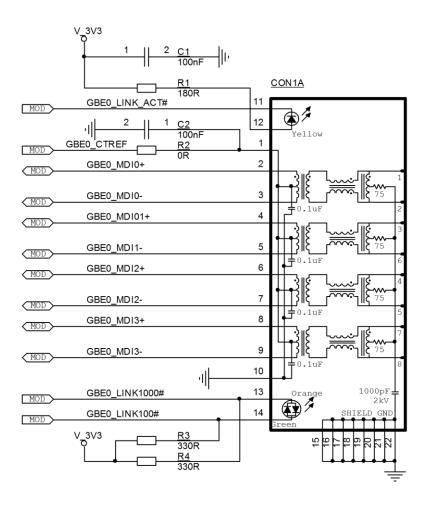

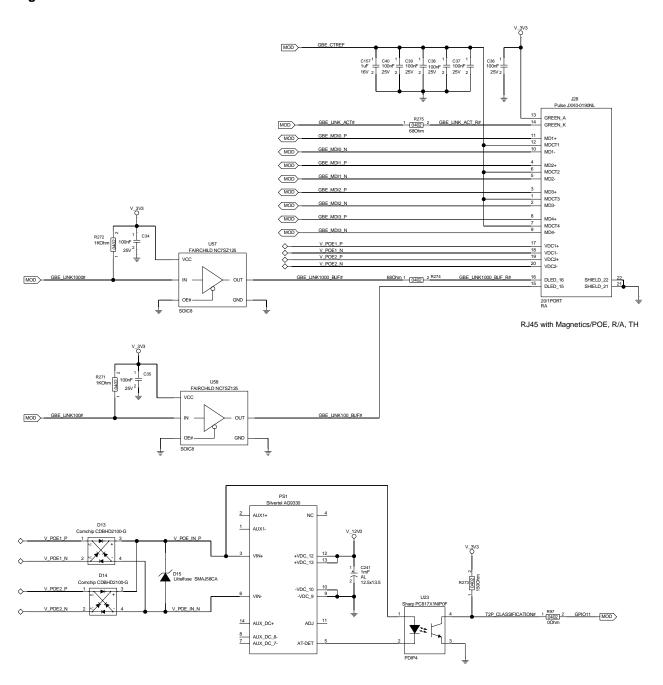

|   | 5.2.1   | GBE Carrier Connector Implementation Example      |      |

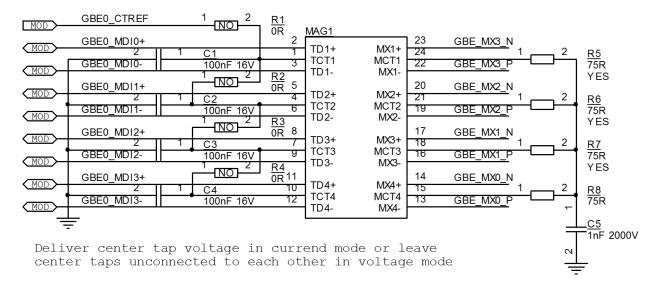

|   | 5.2.2   | GBE Mag-Jack Connector Recommendations            |      |

|   | 5.2.3   | GBE LEDs                                          |      |

|   | 5.2.4   | GBE software-defined Pins                         |      |

|   |         | Cle                                               |      |

|   | 5.3.1   | General                                           |      |

|   | 5.3.2   | PCIe x1 Device Down on Carrier                    |      |

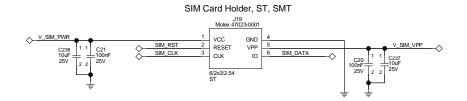

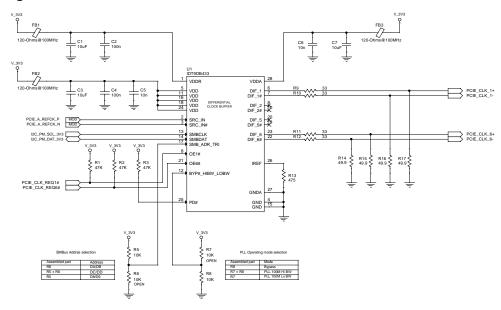

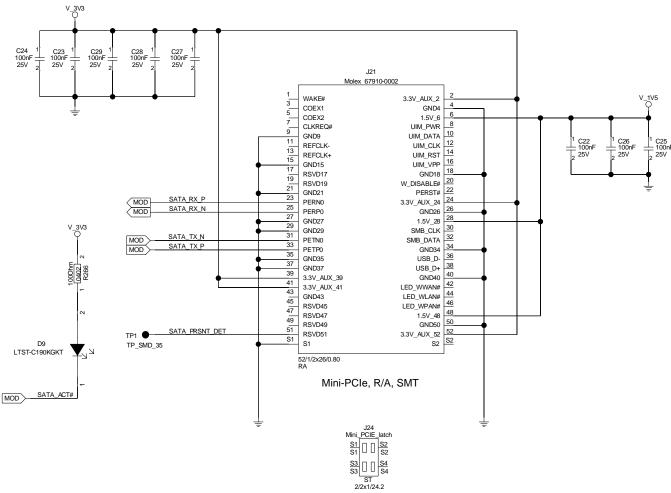

|   | 5.3.3   | Mini-PCIe                                         |      |

|   | 5.3.4   | PCIe Reference Clock buffer                       |      |

|   |         | \ТА                                               |      |

|   | 5.4.1   | General                                           |      |

|   | 5.4.2   | mSATA / MO-300                                    |      |

|   |         | 2                                                 |      |

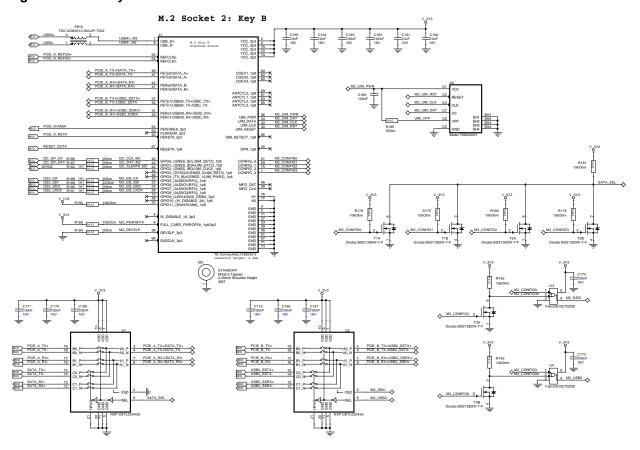

|   | 5.5.1   | B keying                                          |      |

|   |         | M keying                                          |      |

| _ | 5.5.3   | E keying                                          |      |

| j |         | y Card Interfaces                                 |      |

| _ | -       | ) Card                                            |      |

| 1 |         | a Interfaces                                      |      |

|   |         | eneral                                            |      |

|   |         | amera Data Interface Formats                      |      |

|   |         | amera Sensors and Camera Module Vendors           |      |

|   |         | erial Camera Interface Example                    |      |

|   |         | her Camera Options                                |      |

| 3 |         |                                                   |      |

|   |         | MARC Module Native GPIO                           |      |

|   |         | PIO Expansion                                     |      |

| 9 |         | Power Circuits                                    |      |

|   |         | ower Budgeting                                    |      |

|   |         | out Power Sources                                 |      |

|   |         | ower Budgeting, Continued – Fixed 5V Power Source |      |

|   |         | xed 5V DC Power Input Circuit Example             |      |

|   | 9.5 Pc  | ower Hot Swap Controller                          | . 96 |

| 9.6  | High Voltage LED Supply                                 | 97  |

|------|---------------------------------------------------------|-----|

| 9.7  | 3.0V to 5.25V Power Input Example                       |     |

| 9.8  | 12V Input                                               |     |

| 9.9  | Wide Range Power Input                                  |     |

| 9.10 | Power Monitoring                                        | 100 |

| 9.11 | Power Over Ethernet                                     |     |

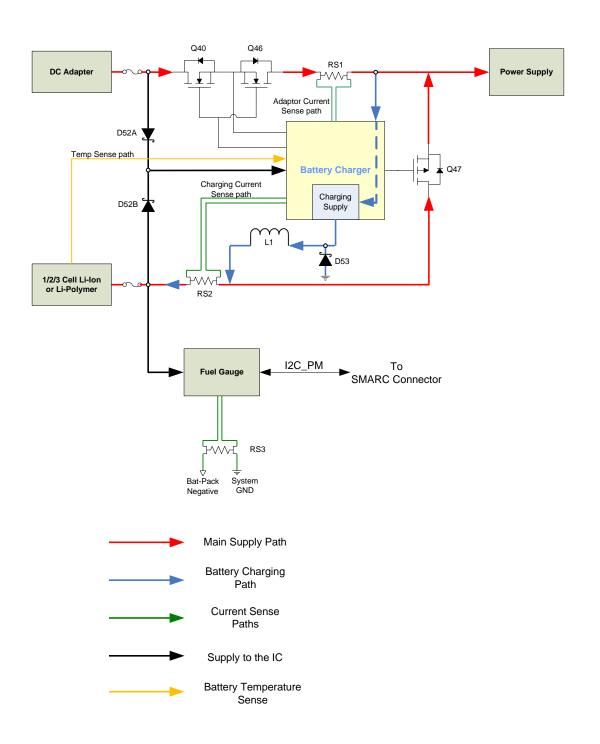

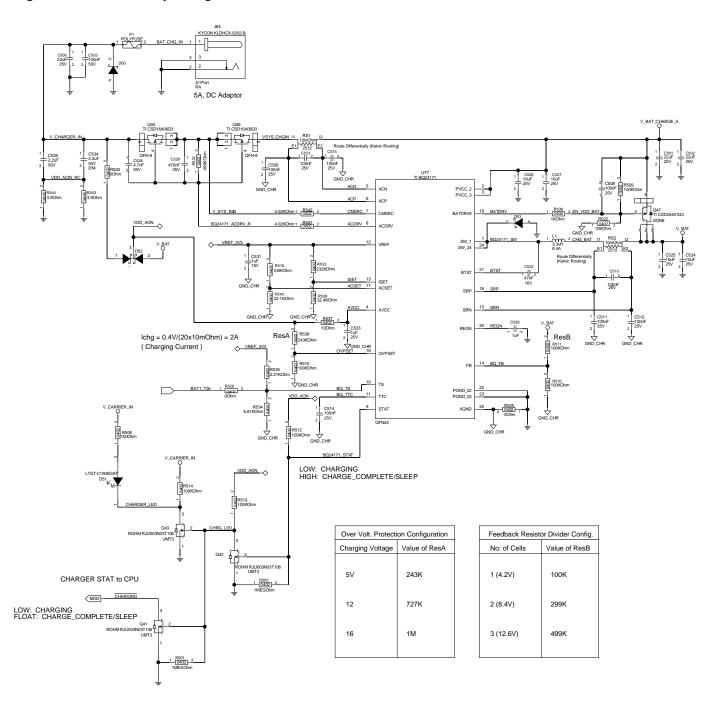

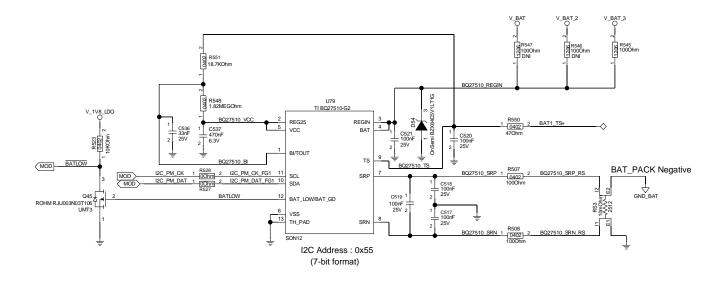

| 9.12 | Li-ION Battery Charger                                  | 104 |

| 9.1  | 2.1 General                                             | 104 |

| 9.1  | 2.2 Battery Charger Circuit Example                     | 105 |

| 10 T | Thermal Management                                      |     |

| 10.1 | General                                                 |     |

| 10.2 | Heat Spreaders                                          | 109 |

| 10.3 | Heat Sinks                                              | 111 |

| 10.4 | Thermal Resistance Calculations                         | 112 |

| 11 ( | Carrier PCB Design Rule Summary                         | 113 |

| 11.1 | General – PCB Construction Terms                        | 113 |

| 11.2 | Differential Pair Cautions                              | 114 |

| 11.3 | General Routing Rules and Cautions                      | 115 |

| 11.4 | Trace Parameters for High-Speed Differential Interfaces | 116 |

| 11.5 | Trace Parameters for Single Ended Interfaces            | 117 |

| 11.6 | PCB Construction Suggestions                            | 118 |

# **FIGURES**

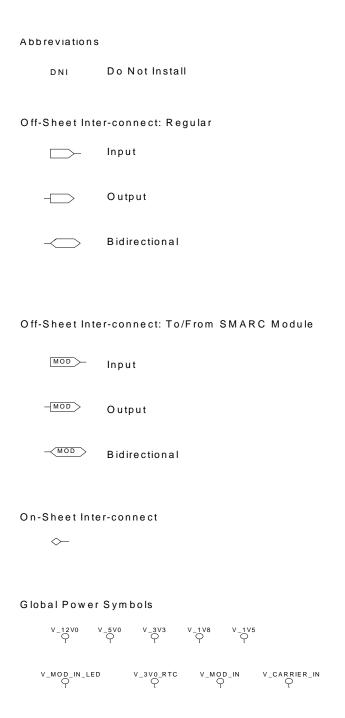

| Figure 1  | Schematic Symbol Conventions                                   | 16             |

|-----------|----------------------------------------------------------------|----------------|

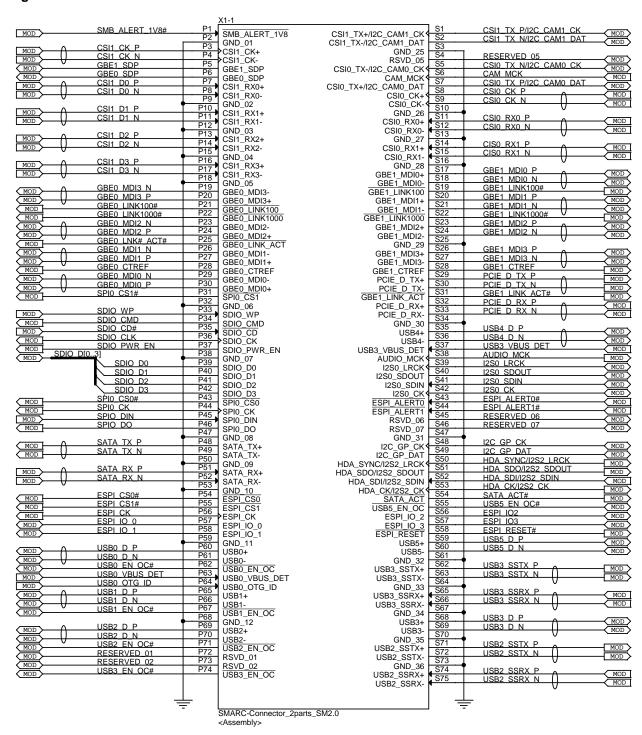

| Figure 2  | Module Connector Pins P1-74 and S1-75                          | 19             |

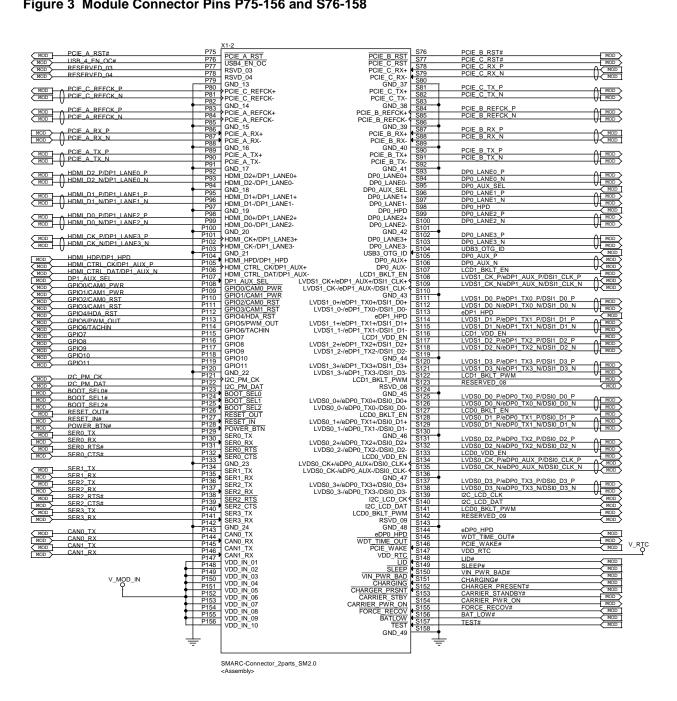

| Figure 3  | Module Connector Pins P75-156 and S76-158                      | 20             |

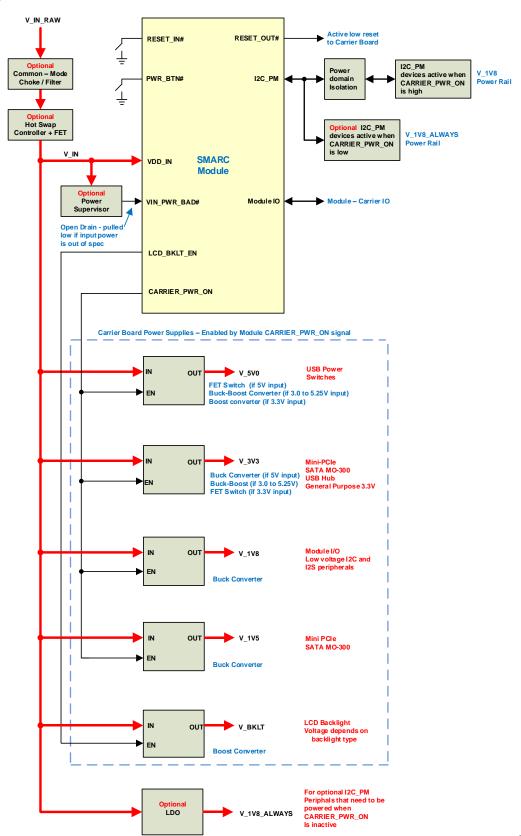

| Figure 4  | Basic Module and Carrier Power Path                            | 22             |

|           | Reset Switch                                                   |                |

| Figure 6  | Power Button Switch                                            | 25             |

| Figure 7  | Force Recovery Switch                                          | 26             |

| Figure 8  | SMARC Carrier Power up Sequence - No Power Button Case         | 27             |

|           | SMARC Carrier Power up Sequence - With Power Button Case       |                |

|           | Boot Selection Jumpers                                         |                |

|           | RTC Backup: Coin Battery / Super Cap                           |                |

|           | Module LVDS: NEC Single Channel Display                        |                |

|           | LVDS Dual Channel                                              |                |

|           | LVDS Dual Channel Power Supply                                 |                |

|           | Carrier EDID EEPROM                                            |                |

|           | HDMI Implementation                                            |                |

|           | DisplayPort ++                                                 |                |

|           | HDMI over DP++                                                 |                |

|           | Embedded DisplayPort (eDP)                                     |                |

|           | MIPI DSI                                                       |                |

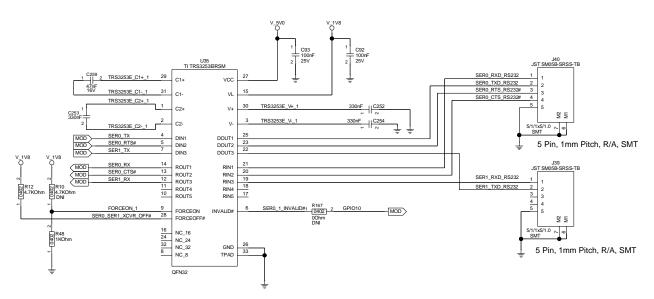

| Figure 21 | Asynchronous Serial Port Transceiver – RS232 – TRS3253E        | 42             |

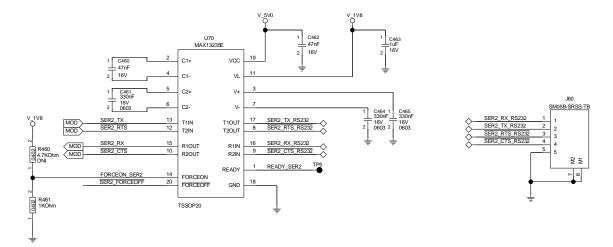

| Figure 22 | Asynchronous Serial Port Transceiver – RS232 – MAX13235E       | 43             |

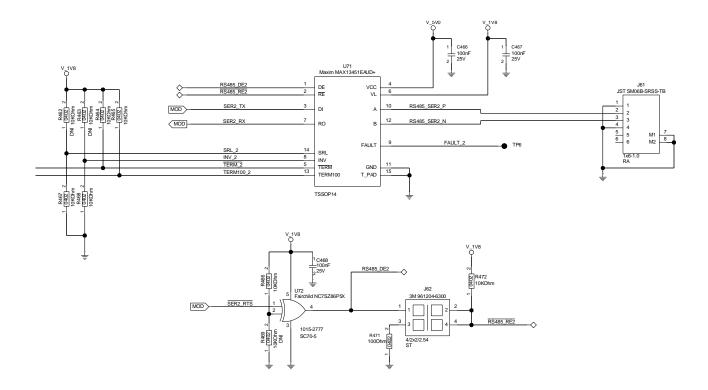

|           | Asynchronous Serial Port Transceiver - RS485 – Half Duplex     |                |

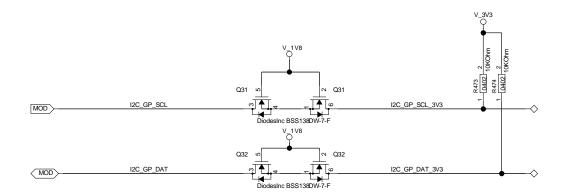

|           | I2C Power Domain Isolation – using FETs                        |                |

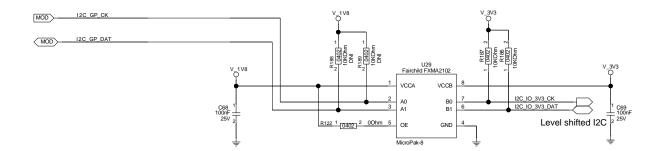

| Figure 25 | I2C Power Domain Isolation and Buffer – Fairchild FXMA2102     | 46             |

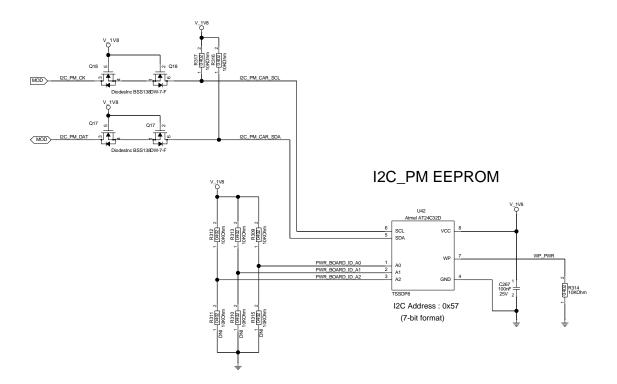

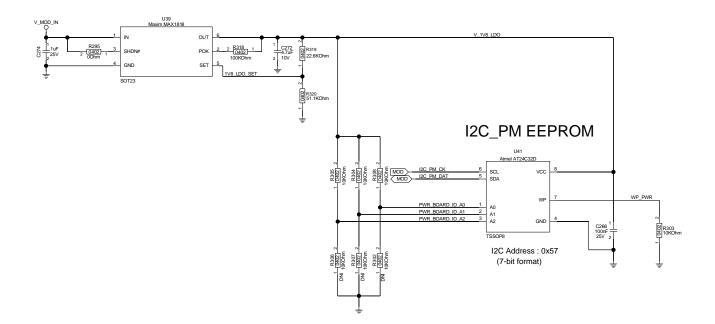

| Figure 26 | I2C_PM EEPROM: Carrier Power Domain                            | 47             |

| Figure 27 | I2C_PM EEPROM: Module Power Domain                             | √1             |

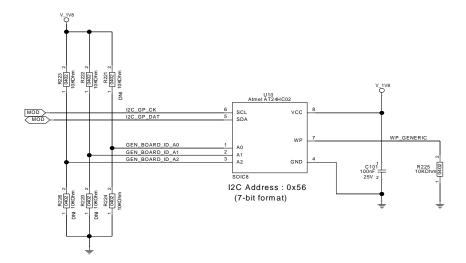

|           | I2C_GP EEPROM                                                  |                |

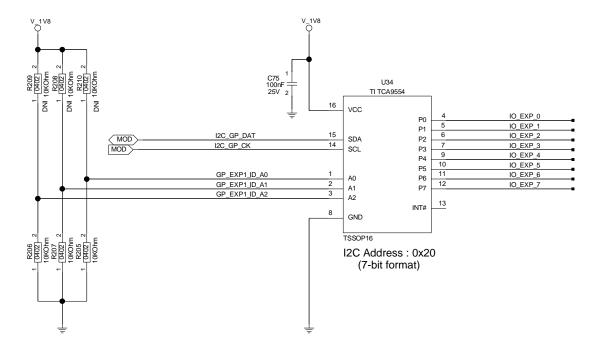

| Figure 20 | I2C Device: I/O Expander                                       | <del>7</del> 0 |

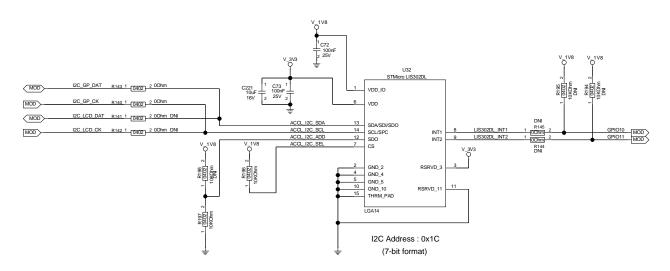

| Figure 30 | I2C Device: Accelerometer                                      | 50<br>51       |

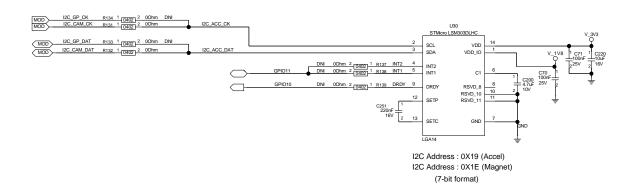

|           | I2C Device: Accelerometer and Magnetometer                     |                |

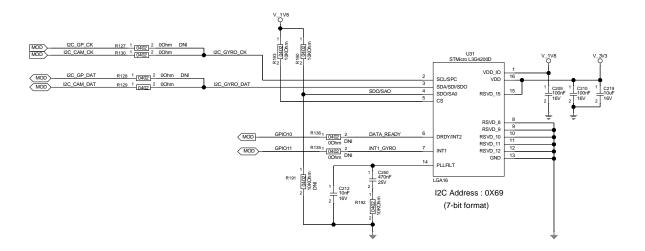

|           | I2C Device: Gyroscope                                          |                |

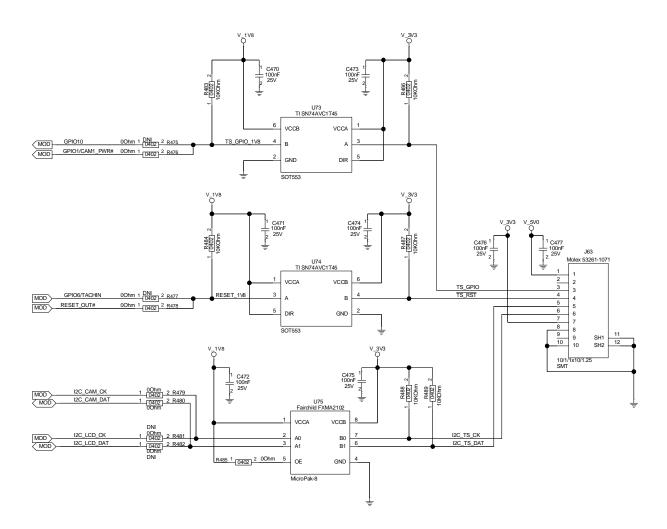

| Figure 32 | Touch Screen Connector – I2C Interface                         | 52<br>55       |

| Figure 34 | I2S Audio Codec Cirrus Logic WM8904                            | 56             |

|           | I2S Audio CODEC: Texas Instruments                             |                |

| Figure 36 | Audio Amplifier: Texas Instruments                             | 51<br>57       |

|           | HD Audio                                                       |                |

|           | Audio switch                                                   |                |

|           | SPI Flash Socket                                               |                |

|           | CAN Bus Implementation                                         |                |

|           | USB0 Client / Host Direct From Module                          |                |

| Figure 41 | USB1 and USB4 Host Ports Direct From Module                    | 05             |

|           | USB 3.0 host dual                                              |                |

|           | USB 3.0 OTG                                                    |                |

| _         |                                                                |                |

|           | USB Hub (1 of 2)USB Hub (2 of 2)                               |                |

|           |                                                                |                |

|           | GBE without POE                                                |                |

|           | GBE separate magnetic for current and voltage mode line driver |                |

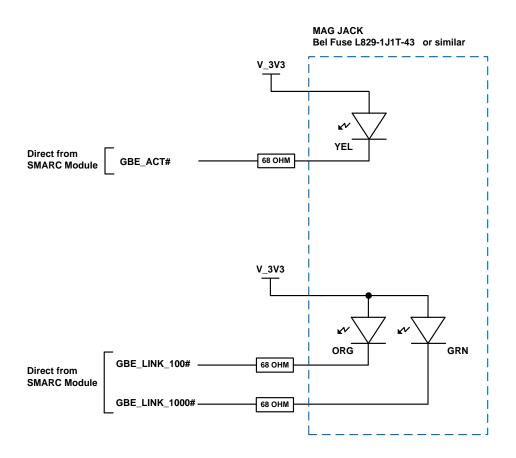

|           | GBE LED Current Sink                                           |                |

|           | GBE LED Current Sink / Source                                  |                |

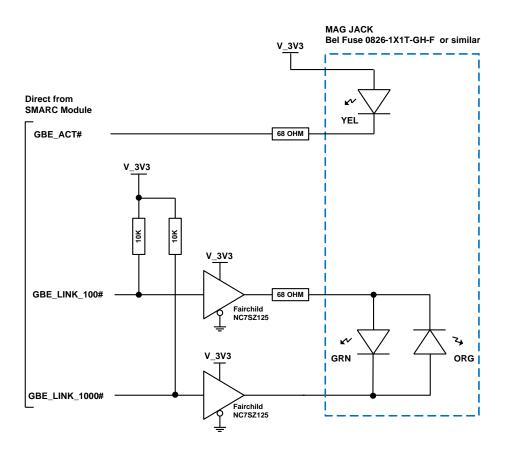

| •         | Interfacing a PCIe x1 Carrier Board Device                     |                |

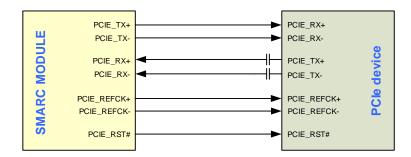

|           | Mini-PCle Slot                                                 |                |

|           | PCIe Clock buffer                                              |                |

| rigure 54 | mSATA / MO-300                                                 | 82             |

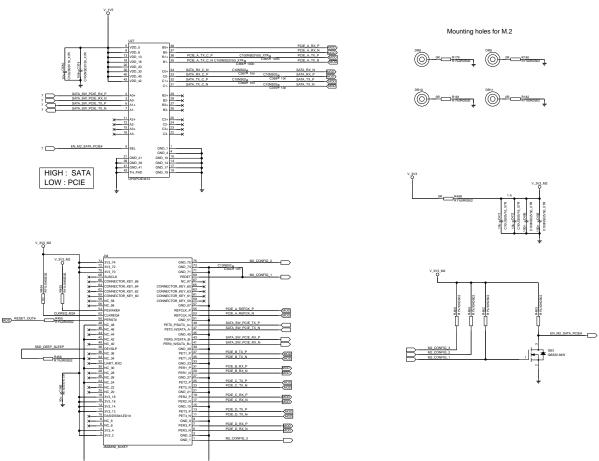

| Figure 56 M.2 Key M                                     | 83                                                             |

|---------------------------------------------------------|----------------------------------------------------------------|

|                                                         |                                                                |

| Figure 57 M.2 Key E                                     |                                                                |

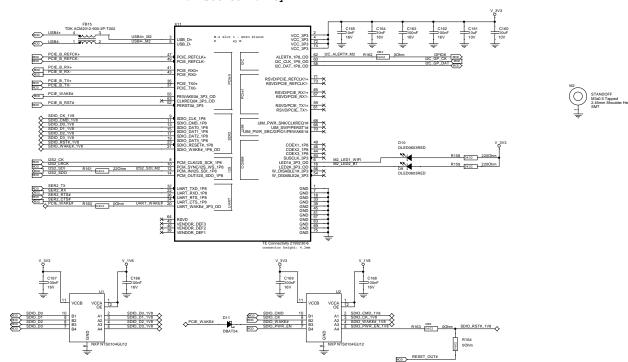

| Figure 58 Micro SD Card Implementation                  |                                                                |

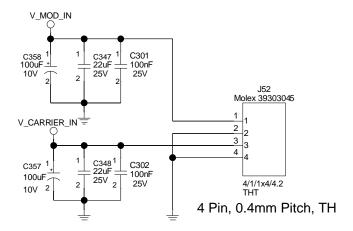

| Figure 59 Serial Camera Implementation                  |                                                                |

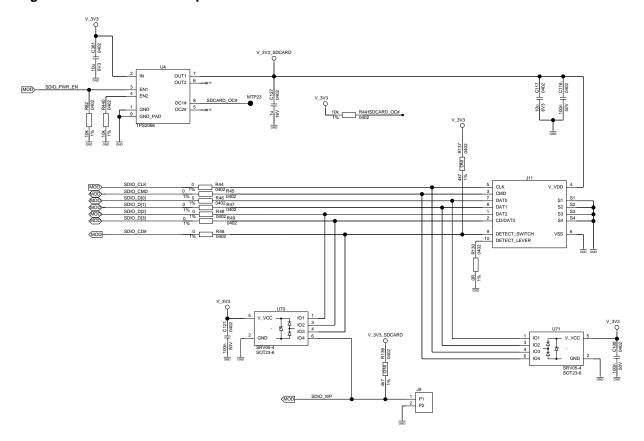

| Figure 60 5V Input Connector                            |                                                                |

| Figure 61 5V Carrier Power Switch                       |                                                                |

| Figure 62 3.3V 2A Buck Converter                        |                                                                |

| Figure 63 1.8V Buck Converter                           |                                                                |

| Figure 64 1.5V Buck Converter                           |                                                                |

| Figure 65 12V Boost Converter for Backlight Power       |                                                                |

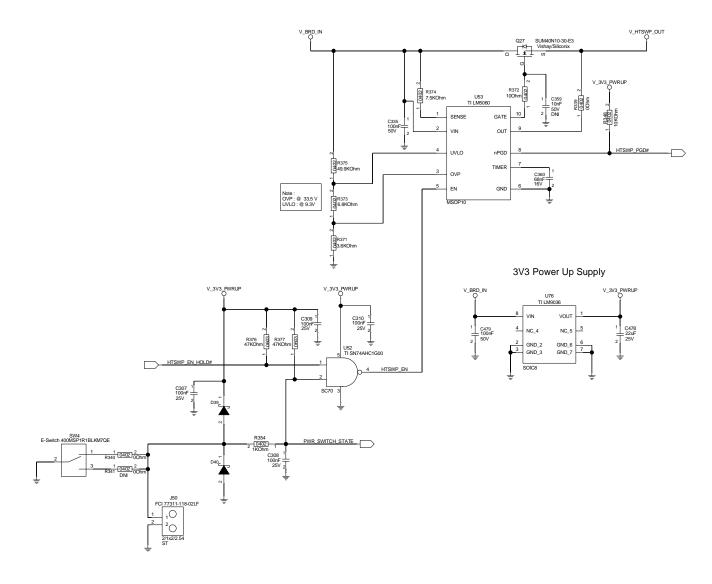

| Figure 66 Hot Swap Controller                           |                                                                |

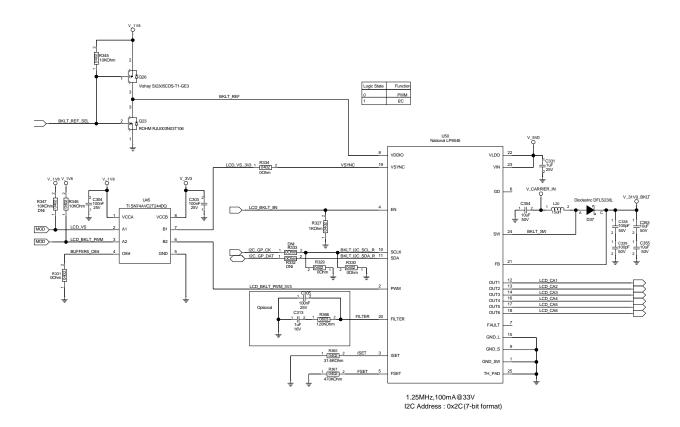

| Figure 67 LP8545 LED Backlight Power                    |                                                                |

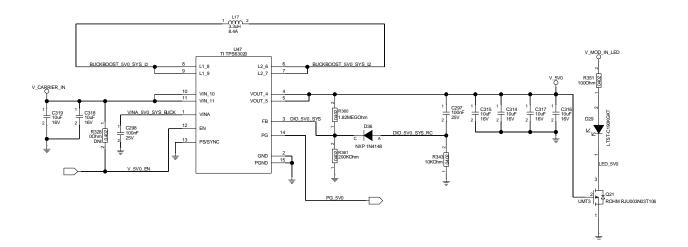

| Figure 68 5V, 2A Buck-Boost Converter                   |                                                                |

| Figure 69 3.3V 2A Buck-Boost Converter                  |                                                                |

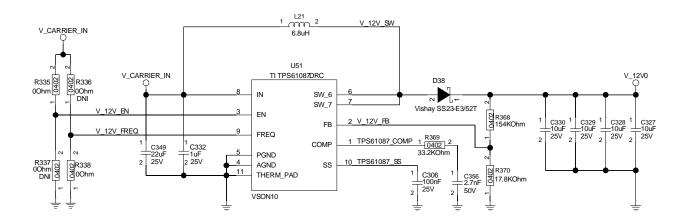

| Figure 70 12V Step Down Switcher                        |                                                                |

| Figure 71 Wide Range Power Input Switcher               |                                                                |

| Figure 72 Power Monitor - Incoming Power                |                                                                |

| Figure 73 GbE with PoE                                  |                                                                |

| Figure 74 Li-ION Battery Charger - Block Diagram        |                                                                |

| Figure 75 Li-ION Battery Charger - Schematic            |                                                                |

| Figure 76 Battery Fuel Gauge                            |                                                                |

| Figure 77 Charger Present Detection                     |                                                                |

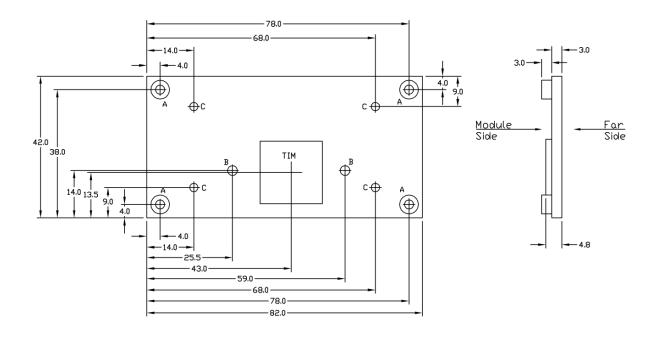

| Figure 78 Heat Spreader Example – 82mm x 50mm Module    |                                                                |

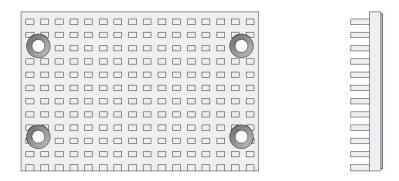

| Figure 79 Heat Sink Add-On to Heat Spreader             |                                                                |

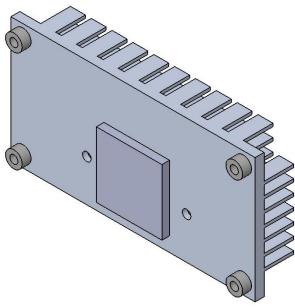

| Figure 80 Stand-Alone Heat Sink                         |                                                                |

|                                                         |                                                                |

| Table 1 Schematic Power Net Naming                      |                                                                |

| Table 2 Boot Select Pins                                |                                                                |

| Table 3 I2C Device Examples - 1.8V I/O                  | 52                                                             |

| Table 4 Popular Touch Technologies                      |                                                                |

| Table F. Taylah Cantrollar Madula / IC / Caraan Vandara | 53                                                             |

| Table 5 Touch Controller Module / IC / Screen Vendors   | 53<br>53                                                       |

| Table 6 SPI Device Examples - 1.8V I/O                  | 53<br>53<br>61                                                 |

| Table 6 SPI Device Examples - 1.8V I/O                  | 53<br>53<br>61<br>74                                           |

| Table 6 SPI Device Examples - 1.8V I/O                  | 53<br>61<br>74                                                 |

| Table 6 SPI Device Examples - 1.8V I/O                  |                                                                |

| Table 6 SPI Device Examples - 1.8V I/O                  |                                                                |

| Table 6 SPI Device Examples - 1.8V I/O                  |                                                                |

| Table 6 SPI Device Examples - 1.8V I/O                  | 53<br>53<br>61<br>74<br>77<br>77<br>81<br>81<br>81             |

| Table 6 SPI Device Examples - 1.8V I/O                  | 53<br>53<br>61<br>74<br>77<br>77<br>81<br>81<br>81             |

| Table 6 SPI Device Examples - 1.8V I/O                  | 53<br>53<br>61<br>74<br>77<br>77<br>81<br>81<br>87<br>87       |

| Table 6 SPI Device Examples - 1.8V I/O                  | 53<br>53<br>61<br>74<br>77<br>77<br>81<br>81<br>87<br>87<br>90 |

| Table 6 SPI Device Examples - 1.8V I/O                  | 53<br>53<br>61<br>74<br>77<br>77<br>81<br>81<br>87<br>87<br>90 |

| Table 6 SPI Device Examples - 1.8V I/O                  | 53 53 53 61 74 77 77 81 81 87 90 91                            |

| Table 6 SPI Device Examples - 1.8V I/O                  | 53 53 53 61 74 77 77 81 81 87 90 91 92                         |

| Table 6 SPI Device Examples - 1.8V I/O                  | 53 53 53 61 74 77 77 81 81 87 90 91 92 104                     |

| Table 6 SPI Device Examples - 1.8V I/O                  | 53 53 53 53 61 74 77 77 81 81 87 90 91 92 104 110 112          |

| Table 6 SPI Device Examples - 1.8V I/O                  | 53 53 53 53 61 74 77 77 81 81 87 90 91 104 110 112             |

| Table 6 SPI Device Examples - 1.8V I/O                  | 53 53 53 61 74 77 77 77 81 81 87 90 91 92 104 110 112 113 116  |

| Table 6 SPI Device Examples - 1.8V I/O                  | 53 53 53 61 74 77 77 81 81 87 90 91 92 104 113 116 117         |

#### 1 Introduction

#### 1.1 General Introduction

SMARC ("Smart Mobility Architecture") is a computer Module standard maintained by the SGeT ("Standardization Group for Embedded Technologies"). SMARC Modules are small form factor (82mm x 50mm and 82mm x 80mm), low power (typically <6W) computer Modules that are used on a Carrier board that utilizes a 314 pin 0.5mm pitch right-angle memory socket style connector to host the Module. SMARC Modules may utilize ARM, low power RISC or low power x86 CPUs / SOCs.

The SMARC Modules are specified in the SGeT **Smart Mobility Architecture Hardware Specification 2.0**. The specification document and an errata document are available free of charge from the SGET web site (**www.sget.org**), subject to their terms of use.

Similarly, this **SMARC Design Guide** is available free of charge from the SGET web site, subject to the SGET terms of use.

# 1.2 Purpose of This Document

The primary purpose of this document is to serve as a Design Guide for developers of SMARC Carrier Boards and for SMARC Module customers who wish to have a SMARC based system developed.

A secondary purpose of this document is to serve as a reference to SMARC Module developers, to help them understand the application of the Modules they are developing.

Finally, this document should be valuable to FAEs and Product managers to help them understand the SMARC infrastructure.

# 1.3 Design Help

There are a number of ways to have a SMARC Carrier board developed:

- Design internally, but have your SMARC Module vendor review your design. Make sure to also have the appropriate semiconductor companies review the portions of the design that utilize their components.

- Use a 3<sup>rd</sup> party firm that specializes in SMARC Carrier development. Such resources may be listed on the SGET web page (www.sget.org).

- Contact your SMARC Module vendor. The Module vendor will have an FAE available for advice.

Many vendors will also undertake custom Carrier design projects, for significant opportunities.

# 1.4 Abbreviations and Acronyms Used

|   | ADC        | Analog to Digital Convertor                                                   |                |

|---|------------|-------------------------------------------------------------------------------|----------------|

| • | ADC        | Analog to Digital Converter                                                   |                |

| • | ARM<br>BCT | Advanced RISC Machines Boot Configuration Table                               | www.arm.com    |

| • | BSP        | (software) Board Support Package                                              |                |

| • | CAD        | Computer Aided Design                                                         |                |

| • | CAN        | Controller Area Network                                                       |                |

| • | CPLD       |                                                                               |                |

| • | CODEC      | Coder – Decoder                                                               |                |

| • | CSI        | Camera Serial Interface                                                       | www.mipi.org   |

| • | DAC        | Digital to Analog Converter                                                   | www.iiiipi.org |

| • | DB-9       | Connector, D shaped, B shell size, 9 pins                                     |                |

| • | DDC        | Display Data Channel                                                          |                |

| • | DDI        | Digital Display Interface                                                     |                |

| • | DE         | Differential Ended (signal pair)                                              |                |

| • | DNI        | Do Not Install (component is not loaded)                                      |                |

| • | DP         | DisplayPort                                                                   |                |

| • | DP++       | Dual-mode DisplayPort                                                         |                |

| • | DSP        | Digital Signal Processor                                                      |                |

| • | DSI        | Display Serial Interface                                                      |                |

| • | EDID       | Extended Display Identification Data                                          | www.vesa.org   |

| • | EEPROM     | Electrically Erasable Programmable Read Only Memory                           |                |

| • | eMMC       | Embedded Multi Media Card                                                     | www.jedec.org  |

| • | ESD        | Electro Static Discharge                                                      |                |

| • | FET        | Field Effect Transistor                                                       |                |

| • | FIFO       | First In First Out (buffer memory)                                            |                |

| • | FS         | Full Speed (USB 2.0 12 Mbps)                                                  |                |

| • | GBE        | Gigabit Ethernet                                                              | www.ieee.org   |

| • | Gbps       | Gigabit per second                                                            |                |

| • | GPIO       | General Purpose Input / Output                                                |                |

| • | GPS        | Global Positioning System                                                     |                |

| • | HDA        | High Definition Audio – Intel defined format                                  | www.intel.com  |

| • | HDMI       | High Definition Multimedia Interface Human Interface Device: USB device class | www.hdmi.org   |

| • | HID<br>HS  |                                                                               |                |

| • | IC         | High Speed (USB 2.0 480 Mbps) Integrated Circuit                              |                |

| • | I2C        | Inter-Integrated Circuit                                                      | www.nxp.com    |

| • | I2S        | Inter-Integrated Circuit – Sound                                              | www.nxp.com    |

| • | IEEE       | Institute of Electrical and Electronics Engineers                             | www.ieee.org   |

| • | IO         | Input Output                                                                  | g              |

| • | ISO        | International Organization for Standardization (French)                       | www.iso.org    |

| • | JEDEC      | Joint Electron Device Engineering Council                                     | www.jedec.org  |

| • | JPEG       | Joint Photographic Experts Group                                              | www.jpeg.org   |

| • | LED        | Light Emitting Diode                                                          | <i>n</i> 0 0   |

| • | Li-lon     | Lithium Ion (rechargeable battery technology)                                 |                |

| • | LVDS       | Low Voltage Differential Signaling                                            |                |

| • | M2.5       | Metric 2.5mm                                                                  |                |

| • | M3         | Metric 3.0mm                                                                  |                |

| • | MAC        | Media Access Controller (e.g. logic circuits in GBE)                          |                |

| • | Mbps       | Megabit per second                                                            |                |

| • | MIPI       | Mobile Industry Processor Interface                                           | www.mipi.org   |

| • | MLC        | Multi Level Cell (flash memory reference)                                     |                |

| • | MOD        | Module (the SMARC Module) (schematic notation)                                |                |

|   |            |                                                                               |                |

| • | MO-297      | Module Outline 297 ("Slim SATA" format)                              | www.jedec.org                    |

|---|-------------|----------------------------------------------------------------------|----------------------------------|

| • | MO-300      | Module Outline 300 (mini-PCle Express card format)                   | www.jedec.org                    |

| • | MPEG        | Motion Picture Experts Group                                         | www.mpeg.org                     |

| • | MXM         | Mobile pci eXpress Module                                            | www.mxm-sig.org                  |

| • | MXM3        | MXM Revision 3                                                       |                                  |

| • | NAND        | A high density flash memory technology                               |                                  |

| • | ns          | Nano second (10 E -9)                                                |                                  |

| • | NC          | Not Connected                                                        |                                  |

| • | NXP         | A semiconductor company                                              | www.nxp.com                      |

| • | OS          | Operating System                                                     |                                  |

| • | OTG         | On the Go (USB term – device can be host or client)                  |                                  |

| • | PCB         | Printed Circuit Board                                                |                                  |

| • | PHY         | Physical (transceiver) – drives cable                                |                                  |

| • | PICMG       | PCI Industrial Computer Manufacturing Group                          | www.picmg.org                    |

| • | PCI<br>PCIe | Peripheral Component Interface                                       | www.pcisig.org                   |

| • | PCI-SIG     | PCI Express PCI Special Interest Group                               | www.pcisig.org<br>www.pcisig.org |

| • | PCM         | Pulse-Code Modulation                                                | www.pcisig.org                   |

| • | PLL         | Phase Locked Loop                                                    |                                  |

| • | POE         | Power Over Ethernet                                                  |                                  |

| • | ps          | Pico second (10 E -12)                                               |                                  |

| • | PWM         | Pulse Width Modulation                                               |                                  |

| • | RGB         | Video data in Red Green Blue pixel format                            |                                  |

| • | RISC        | Reduced Instruction Set Computing                                    |                                  |

| • | ROM         | Read Only Memory                                                     |                                  |

| • | RS232       | Recommend Standard 232 (asynchronous serial ports)                   |                                  |

| • | RS485       | Asynchronous serial data, differential, multidrop                    |                                  |

| • | RTC         | Real Time Clock (battery backed clock and memory)                    |                                  |

| • | SAR         | Successive Approximation Register                                    |                                  |

| • | SATA        | Serial ATA (serial mass storage interface)                           | www.sata-io.org                  |

| • | SD          | Secure Digital (memory card)                                         |                                  |

| • | SE          | Single Ended (signal, as opposed to differential)                    |                                  |

| • | SGeT        | Standardization Group for Embedded Technologies                      | www.sget.org                     |

| • | SLC         | Single Level Cell (flash memory reference)                           |                                  |

| • | SMARC       | Smart Mobility Architecture                                          | www.sget.org                     |

| • | SMSC        | A semiconductor company, now MICROCHIP                               | www.smsc.com                     |

| • | SOC         | System On Chip                                                       |                                  |

| • | S/PDIF      | Sony/Philips Digital Interconnect Format                             |                                  |

| • | SPI<br>SSD  | Serial Peripheral Interface<br>Solid State Disk                      |                                  |

| • | 33D<br>TI   |                                                                      | www.ti.com                       |

| • | TIM         | Texas Instruments – semiconductor company Thermal Interface Material | www.ti.com                       |

| • | UART        | Universal Asynchronous Receiver Transmitter                          |                                  |

| • | UL          | Underwriters Laboratories                                            | www.ul.com                       |

| • | USB         | Universal Serial Bus                                                 | www.usb.org                      |

| • | VESA        | Video Electronics Standards Association                              | www.vesa.org                     |

| • | WEC7        | Windows Embedded Compact 7 (an OS)                                   |                                  |

| • | YUV         | Video data format, more common in television                         |                                  |

| • | X5R         | Ceramic capacitor dielectric – good quality                          |                                  |

| • | X7R         | Ceramic capacitor dielectric – best quality                          |                                  |

| • | X86         | Intel architecture (80x86) CPUs                                      |                                  |

|   |             | , ,                                                                  |                                  |

#### 1.5 Document References

#### 1.5.1 SGET Documents

Smart Mobility Architecture Hardware Specification, V 2.0, June 2, 2016 © SGET (Standardization Group For Embedded Technologies) www.sget.org

#### 1.5.2 Industry Standards Documents

- BT.656 ("Recommendation ITU-R BT.656-5 Interface for digital component video signals in 525-line and 625-line television systems operating at the 4:2:2 level of Recommendation ITU-R BT.601"), International Telecommunications Union, December 2007 (www.itu.int)

- CAN ("Controller Area Network") Bus Standard ISO 11898

- **CSI-2** (**Camera Serial Interface version 2**) The CSI-2 standard is owned and maintained by the MIPI Alliance ("Mobile Industry Processor Interface Alliance") (**www.mipi.org**).

- CSI-3 (Camera Serial Interface version 3) The CSI-3 standard is owned and maintained by the MIPI Alliance ("Mobile Industry Processor Alliance") (www.mipi.org)

- COM Express the formal title for the COM Express specification is "PICMG® COM.0 COM

Express Module Base Specification", Revision 2.1, May 14, 2012. This standard is owned and

maintained by the PICMG ("PCI Industrial Computer Manufacturer's Group") (www.picmg.org)

- DisplayPort and Embedded DisplayPort These standards are owned and maintained by VESA ("Video Electronics Standards Association") (www.vesa.org)

- D-PHY CSI-2 physical layer standard owned and maintained by the MIPI Alliance (www.mipi.org)

- DSI (Display Serial Interface) The DSI standard is owned and maintained by the MIPI Alliance ("Mobile Industry Processor Alliance") (www.mipi.org)

- **eMMC** ("**Embedded Multi-Media Card**") the eMMC electrical standard is defined by JEDEC JESD84-B45 and the mechanical standard by JESD84-C44 (**www.jedec.org**).

- eSPI ("Enhanced Serial Peripheral Interface") The eSPI Interface Base Specification is defined by Intel (https://downloadcenter.intel.com/de/download/22112)

- **Fieldbus** this term refers to a number of network protocols used for real time industrial control. Refer to the following web sites: www.profibus.com/downloads and www.canopen.org

- GBE MDI ("Gigabit Ethernet Medium Dependent Interface") defined by IEEE 802.3. The 1000Base-T operation over copper twisted pair cabling defined by IEEE 802.3ab (www.ieee.org).

- HDA (HD Audio), High Definition Audio Specification, Intel, Revision 1.0a, June 17, 2010 (http://www.intel.com/content/dam/www/public/us/en/documents/product-specifications/high-definition-audio-specification.pdf)

- HDMI Specification, Version 1.3a, November 10, 2006 © Hitachi and other companies (www.hdmi.org).

- The I2C Specification, Version 2.1, January 2000, Philips Semiconductor (now NXP) (www.nxp.com).

- *I2S Bus Specification,* Feb. 1986 and Revised June 5, 1996, Philips Semiconductor (now NXP) (www.nxp.com).

- IEEE1588 2008. IEEE Standard for a Precision Clock Synchronization Protocol for Networked Measurement and Control Systems (http://standards.ieee.org/findstds/standard/1588-2008.html)

- JTAG ("Joint Test Action Group") This is defined by IEEE 1149.1-2001 IEEE Standard Test Access Port and Boundary Scan Architecture (www.ieee.org)

- JEDEC MO-300 (mSATA) defines the physical form factor of the mSATA format (www.jedec.org). The electrical connections are defined in the Serial ATA document.

- MXM3 Graphics Module Mobile PCI Express Module Electromechanical Specification, Version 3.0, Revision 1.1, © 2009 NVidia Corporation (www.mxm-sig.org).

- PICMG® EEEP Embedded EEPROM Specification, Rev. 1.0, August 2010 (www.picmg.org).

- PCI Express Specifications (www.pci-sig.org).

- PCI Express Mini Card Electromechanical Specification Revision 2.0, April 21, 2012, © PCI-SIG (www.pci-sig.org).

- RS-232 (EIA "Recommended Standard 232") this standard for asynchronous serial port data

exchange dates from 1962. The original standard is hard to find. Many good descriptions of the

standard can be found on-line, e.g. at Wikipedia, and in text books.

- **Serial ATA Revision 3.1**, July 18, 2011, Gold Revision, © Serial ATA International Organization (www.sata-io.org).

- **SD Specifications Part 1 Physical Layer Simplified Specification,** Version 3.01, May 18, 2010, © 2010 SD Group and SD Card Association ("Secure Digital") (www.sdcard.org).

- **SM Bus** "System Management Bus" Specification Version 3.0, 2© 2014 System Management Interface Forum, Inc. (http://www.smbus.org)

- SPDIF (aka S/PDIF) ("Sony Philips Digital Interconnect Format) IEC 60958-3.

- SPI Bus "Serial Peripheral Interface" de-facto serial interface standard defined by Motorola. A

good description may be found on Wikipedia

(http://en.wikipedia.org/wiki/Serial\_Peripheral\_Interface\_Bus).

- UL 1642 Lithium Batteries safety standard governing the use of lithium batteries (www.ul.com)

- USB Specifications (www.usb.org).

- VESA Enhanced Extended Display Identification Data Standard, Rev. 1, Feb 9, 2000, VESA (www.vesa.org) See also the "EDID" page on Wikipedia.

# 1.6 Schematic Example Correctness

The schematic examples shown in this Design Guide are believed to be correct but correctness cannot be guaranteed. Most of the examples have been pulled from designs that have been built, tested, and are known to work. Most of them have been re-formatted to fit better in this design guide.

# 1.7 Software Support

Many hardware examples and suggestions are given in the following pages. SMARC Carrier hardware design is generally straightforward. However, before committing to a particular hardware selection, it is wise to check out the software driver support. A particular device may be supported in, say, for example, Linux but not in Windows. Your overall project may go smoother if you pick out hardware that already has software support in your target OS.

There are various possible sources for software drivers for a particular IC: the IC vendor, the OS vendor, the OS community, your Module vendor, your Carrier design partner, other independent sources and of course writing your own.

Most SMARC Module vendors offer a BSP (Board Support Package) for their Module. Your target Carrier device may be supported in the BSP – check this angle out as well.

# 1.8 Schematic Example Conventions

Some of the conventions used in the schematic examples are described below. Note off-page connections that tie directly to the SMARC Module have the notation "MOD" in the off-page connect symbol.

Figure 1 Schematic Symbol Conventions

# **Table 1 Schematic Power Net Naming**

| V_IN_RAW                                                                                                  | Power in to the overall system, before any filtering, fusing, polarity or rise time protection                                                                                                                          |  |

|-----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| V_IN                                                                                                      | Power in to the overall system, after (optional) filtering, fusing, polarity or rise time protection                                                                                                                    |  |

| V_MOD_IN                                                                                                  | Power into the SMARC Module. It must be within the 3.0V to 5.25V range defined by the SMARC specification                                                                                                               |  |

| V_CARRIER_IN Power in to the Carrier Board. It may be the same as V_MOD_IN, dependent the design at hand. |                                                                                                                                                                                                                         |  |

|                                                                                                           | On SMARC Evaluation Carrier boards, V_CARRIER_IN is sometimes kept separate from V_MOD_IN to allow easier measurements and tracking of where the power goes.                                                            |  |

| V_5V0                                                                                                     | 5V supply on the Carrier Board                                                                                                                                                                                          |  |

| V_3V3                                                                                                     | 3.3V supply on the Carrier Board                                                                                                                                                                                        |  |

| V_1V8                                                                                                     | 1.8V supply on the Carrier Board                                                                                                                                                                                        |  |

| V_1V5                                                                                                     | 1.5V supply on the Carrier Board                                                                                                                                                                                        |  |

| V_3V0_RTC                                                                                                 | Supply voltage from the Carrier Board to the SMARC VDD_RTC pin (pin S147) This is a low voltage, low current supply separate from V_MOD_IN, used to supply the Module RTC (Real Time Clock) in the absence of V_MOD_IN. |  |

| V_MOD_IN_LED                                                                                              | Same as V_MOD_IN except isolated by a series jumper – used for power status LEDs – jumper can be removed to prevent status LEDs from consuming power                                                                    |  |

# 2 INFRASTRUCTURE: CONNECTOR, POWER DELIVERY, SYSTEM MANAGEMENT

#### 2.1 Module Connector

The SMARC Module connector is well described in the **Smart Mobility ARChitecture Hardware Specification** 2.0 and the complete description is not repeated here.

Briefly, the SMARC Module connector is a low profile, right angle 314 pin memory – socket style connector. The same connector is commonly used for MXM3 graphics cards. However, it is important to understand that the SMARC usage and pin-out of this connector is totally different from the usage as graphics card.

The SMARC Module connector is available from multiple sources, including at least one vendor that has qualified their offering for automotive use.

Various height profiles are available for the SMARC Module connector. The lowest profile available has a Carrier Board PCB top-side to Module PCB bottom-side separation of 1.5mm, and a connector body height of 4.3mm.

Figure 2 Module Connector Pins P1-74 and S1-75

Figure 3 Module Connector Pins P75-156 and S76-158

#### 2.2 Module Power

#### 2.2.1 Input Voltage Range

Per the SMARC Module Hardware Specification, the SMARC Modules may accept input power over the voltage range 3.0V to 5.25V. This range coincides with the range of a single-level lithium – ion cells and allows the use of common 5V or 3.3V fixed DC supplies.

## 2.2.2 Input Voltage Rise Time

There are currently no limits in the SMARC Module Hardware Specification on the Module power supply rise times. In general, it is not wise to expose the Module and Carrier electronics to extremely fast power supply rise times (as may be the case if a low impedance power source such as a battery pack or power brick is "hot-plugged"). Input power supply rise times faster than 50V / millisecond to the Module should be avoided. If a unit is to be "hot-plugged" to a low impedance power source, then the Carrier should implement measures to slow the power rise time as seen by the Module and Carrier circuits. The Carrier can do this by implementing a FET and hot-swap controller in the input power path. This is discussed in Section 9.5 Power Hot Swap Controller.

#### 2.2.3 Module Maximum Input Power

The SMARC V2.0 specification document states that the allowable input voltage range is 3.0V to 5.25V. The rationale for this is that this range coincides with the voltage range of single level lithium-ion cells, and that it also allows the use of common 5V or 3.3V bench supplies. However, it is not mandatory in the V2.0 specification that Modules are required to work at the lower end (3.0V) of this range.

The SMARC Module physical connector is a MXM3 connector (although the pinout is completely different). The MXM3 specification document requires that the MXM3 connector pins be able to carry 0.5A current minimum. SMARC Modules allocate 10 pins for input power (and 49 GND pins for signal and power return). Thus, per the MXM3 connector requirement, the 10 pins should be capable of handling 5A. This allows a maximum power input range of 15W (for 3.0V power in) to 26W (for 5.25V power in).

For conservative design, let us operate the MXM3 connector pins at no more than 70% of their capacity. Then the following maximum power inputs are achieved:

```

10 pins * 0.5A * 70% * 3.0V = 10.5W (low end of Li-Ion battery)

10 pins * 0.5A * 70% * 4.75V = 16.6W (low end of 5V bench supply)

```

These numbers apply to the Module only, and not to the Carrier circuits. The 10.5W is adequate for low power Modules that are to be served by single level Lithium-Ion cells. The 16.6W should be adequate for higher power Modules (Including x86 designs) operating from a 5V supply.

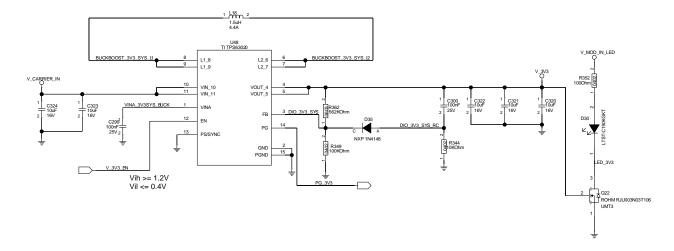

#### 2.2.4 Power Path

The power path for a basic, fixed input voltage arrangement SMARC Module and Carrier board system is shown in **Figure 4 Basic Module and Carrier Power Path** below. A number of features in the figure are optional and may be omitted (and bypassed) in a minimal implementation. The figure also shows Carrier Board power supply sections assuming a typical system powered by a power source in the 3.0V to 5.25V range

Figure 4 Basic Module and Carrier Power Path

## 2.3 Module I/O Voltage

The SMARC Module Hardware Specification specifies the use of 1.8V Module I/O

I/O at 1.8V is used in general for low power interfaces. Many contemporary peripherals of interest are available with I/O interfaces that support 1.8V and 3.3V; some are available at 1.8V only, and others at 3.3V only. Specific examples are given in various document sections below.

If devices that support only 3.3V are implemented, a level shifter has to be used to interface them to the SMARC Module.

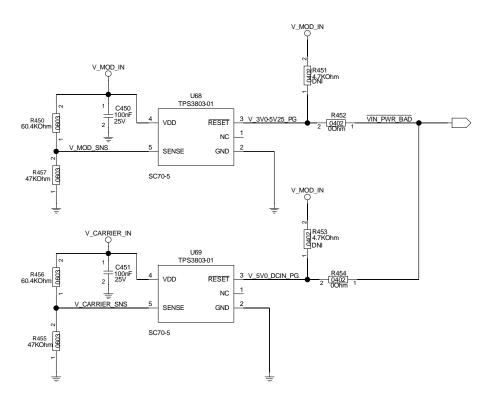

#### 2.4 VIN PWR BAD#

This optional signal may be used to tell the Module that the input power to the Module is not ready. An open-drain driver should be used.

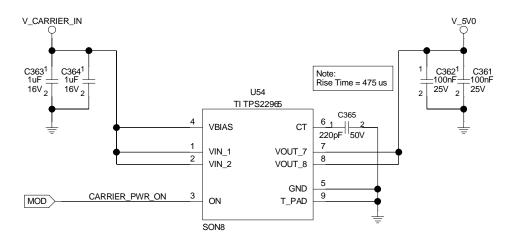

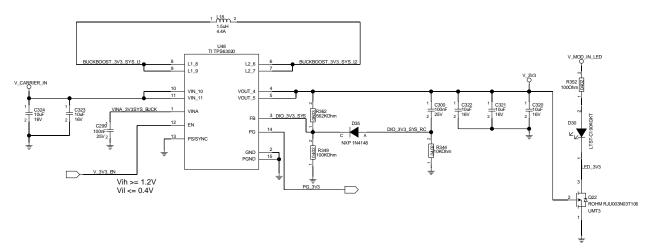

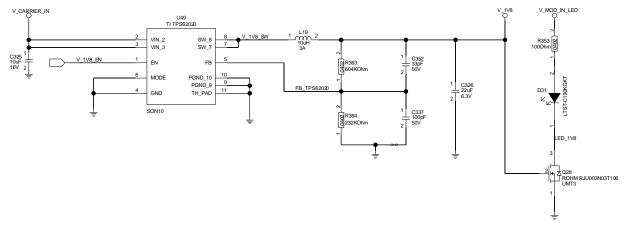

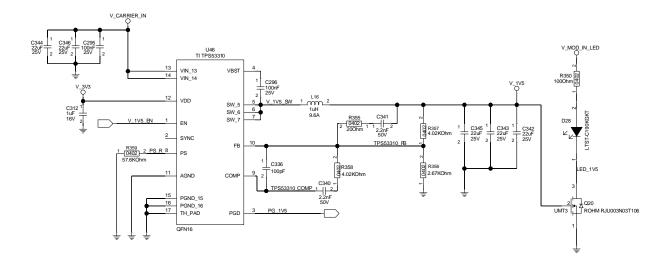

## 2.5 CARRIER PWR ON

The CARRIER\_PWR\_ON signal is driven by the Module at a 1.8V level. It is a signal to Carrier that the Carrier board specific power supplies may be enabled. This is illustrated in **Figure 4 Basic Module and Carrier Power Path** above.

#### 2.6 Reset In to Module

The SMARC RESET\_IN# signal may be used to force a SMARC system reset. It is an input to the Module. The signal is pulled up on the Module. If used, by the Carrier board, then an open drain device or switch to GND should be used. A switch example is shown in the following figure. The signal is ESD protected in this example, as the switch (and the switch interaction with humans) introduces an ESD hazard.

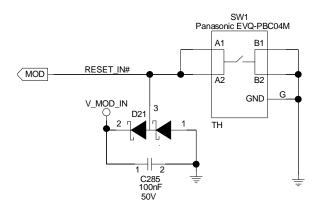

Figure 5 Reset Switch

#### 2.7 Power Button

SMARC defines a pin to allow the implementation of a Carrier based power button. However - caution - the SMARC Hardware Specification does not define the power up behavior of a Module. The following possibilities exist after a cold power on:

- a) Module boots

- b) Module waits for a Power Button press to boot

- c) The Module is configurable either behavior a) or behavior b) may be configured

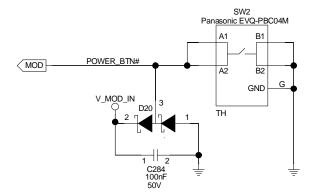

Users are advised to check with your Module vendor on this topic. A Power Button switch example is shown in the figure below. If your Module waits for a Power Button press on power up and you want it to always boot on power up, you have to arrange for a "power button press" on power up, using an open drain device to interface to the SMARC Module.

Figure 6 Power Button Switch

## 2.8 Force Recovery

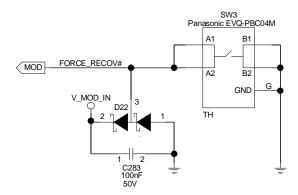

Some Modules support a "force recovery" function in which the primary boot media can be re-initialized over a designated I/O interface, such as a USB client interface, asynchronous serial port, or Ethernet port. This is Module specific; refer to your Module documentation for further details.

Figure 7 Force Recovery Switch

## 2.9 Power Up Sequence

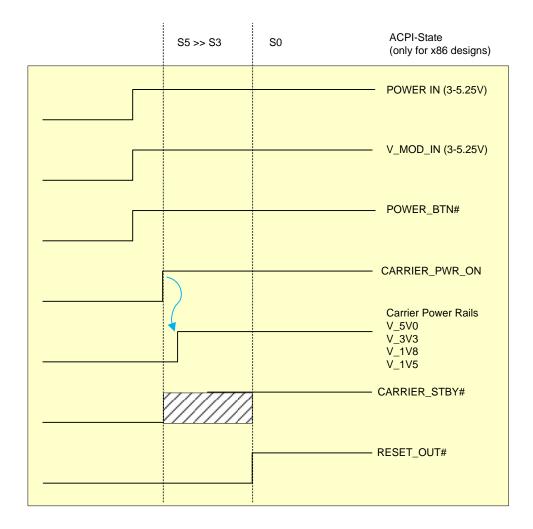

The basic power up sequence for SMARC Modules and Carriers is shown in the following two figures. There is a Module design and / or configuration dependence with regard to the power button behavior. Depending on design and / or configuration, the Module may always boot without waiting for a power button press, or it may wait for a power button press. These cases are shown in the figures.

It is recommended to arrange that the main Carrier power supplies not come up until the Module asserts the CARRIER\_PWR\_ON signal. When this is high, you know that the Module power supplies are all up. If the Carrier power is up before the Module supplies are up, there is a risk that the Carrier circuits will backfeed power to the Module I/O pins, which might interfere with a Module boot.

Figure 8 SMARC Carrier Power up Sequence - No Power Button Case

The case of a Module that is designed or configured to wait for a power button press before it comes up is diagramed below. When power is applied to the Module, in this case, only a small portion of the Module is using that power – typically, the Module Power Management section – and that circuitry waits for a power button press. When it sees one, the Module proceeds with the boot. When the main Module power rails are up, the Module asserts CARRIER\_PWR\_ON. The Carrier should use this signal to enable the various Carrier power rails. However, Carrier circuits that are involved in power management (battery charge level, reset monitors, etc.) may be powered ahead of CARRIER\_PWR\_ON, coincident with the Module power.

**ACPI-State** S5 >> S3 S0 (only for x86 designs) POWER IN (3-5.25V) V\_MOD\_IN (3-5.25V) POWER\_BTN# NOT x86 chipset Power button signal CARRIER\_PWR\_ON Carrier Power Rails V\_5V0 V\_3V3 V\_1V8 V\_1V5 CARRIER\_STBY# RESET\_OUT#

Figure 9 SMARC Carrier Power up Sequence - With Power Button Case

#### 2.9.1 CARRIER\_STBY#

A low level on CARRIER\_STBY# indicates that the system is going into the standby state, where only power management functions and system memory are powered. The ACPI equivalent is suspend to ram (S3). This signal can be used to switch off power supplies on the Carrier board that are not necessarily needed during standby.

Any devices that should be able to wake the system out of the standby state should use the CARRIER\_PWR\_ON signal instead.

#### 2.10 Boot Selection

#### 2.10.1 Boot Definitions

Most SOCs used on SMARC Modules have the following attributes:

- 1) An internal ROM exists. The internal ROM code is executed after the SOC comes out of reset. This ROM code is provided by the silicon vendor and is generally not available or visible to users.

- 2) A set of SOC strap pins is used to select what SOC physical device interface (SD Card, SPI, eMMC, etc.) will be used for the second stage boot process (also known as BCT or Boot Configuration Table boot). There is no commonality between various SOCs as to how the strap pins are defined.

- 3) The SOC pin configuration is very flexible most SOC pins can be used for several functions, and the SMARC Module designer must choose a pin configuration that works for the design at hand. The SOC pin configuration is set by a Boot Configuration Table that is read out from the external boot media (SD Card, SPI, eMMC, etc.).

There are several stages in the boot process:

- 1) Internal SOC ROM execution

- 2) second stage boot, from non-volatile memory external to the SOC: BCT is loaded and various other system parameters are set

- 3) Operating System load

The Operating System load may occur from the same memory as the second stage BCT boot, or the second stage code may pass the Operating System load off to another device, such as a USB drive or SATA drive.

## 2.10.2 SMARC BOOT\_SEL Pins

The SMARC Hardware Specification defines 3 SMARC pins, designated BOOT\_SEL0# through BOOT\_SEL2#, that may be used to tell the Module what physical device to do a BCT boot from. The SMARC BOOT\_SELx# pins serve to abstract the SOC – dependent strap definitions into a common SMARC definition. The table below is reproduced from the SMARC Hardware Specification document.

**Table 2 Boot Select Pins**

|   | Carrier Connection |            |            | Boot Source                                 |

|---|--------------------|------------|------------|---------------------------------------------|

|   | BOOT_SEL2#         | BOOT_SEL1# | BOOT_SEL0# |                                             |

| 0 | GND                | GND        | GND        | Carrier SATA                                |

| 1 | GND                | GND        | Float      | Carrier SD Card                             |

| 2 | GND                | Float      | GND        | Carrier eMMC Flash                          |

| 3 | GND                | Float      | Float      | Carrier SPI                                 |

| 4 | Float              | GND        | GND        | Module device (NAND, NOR) – vendor specific |

| 5 | Float              | GND        | Float      | Remote boot (GBE, serial) – vendor specific |

| 6 | Float              | Float      | GND        | Module eMMC Flash                           |

| 7 | Float              | Float      | Float      | Module SPI                                  |

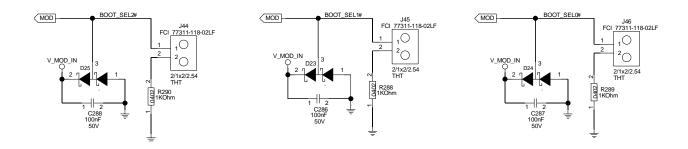

The Module BOOT\_SELx# pins may be set by jumpers on the Carrier Board, as shown in the figure below. The diodes and capacitors are for ESD protection, as the jumpers may experience ESD events.

Alternatively, the BOOT\_SELx# pins can be set by low value option resistors to GND on the Carrier. The resistors are either installed (for a GND connection) or not installed, per the table above.

Figure 10 Boot Selection Jumpers

# 2.11 RTC Backup Power

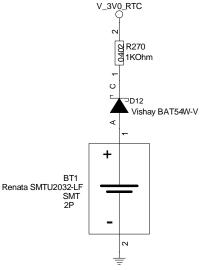

The Module RTC (Real Time Clock) circuit requires a backup power source if the Module RTC circuit is expected to keep time in the absence of the primary power source (i.e. the power to Module VDD\_IN pins, P147 through P156). The RTC backup power, if used, is applied to the Module VDD\_RTC pin, pin S147. The RTC backup power may be provided by a battery or by a large value capacitor, known as a "Supercap".

If a battery is used, the battery is typically a small lithium coin cell with a capacity of a few hundred mAh. Lithium coin cells offer a high energy density, low self-discharge rate, and are not rechargeable. For safety reasons, they must be protected against charging **on the Carrier board** by a redundant set of circuit elements – typically either two diodes in series or a diode and a resistor. The resistor, if used, must be large enough to limit the battery charging current to be equal to or lower than the amount specified as allowable by the battery vendor. The safety aspects of lithium battery use is governed by a UL document (*UL 1642 Lithium Batteries*, www.ul.com).

The Supercap solution differs from the lithium battery solution in that it needs to be charged by the Module (when the Module has its primary power source); hence a blocking diode should not be used with the Supercap.

The time period over which the RTC backup power is effective depends on the Module RTC backup current draw, the exact voltage range over which the Module RTC circuit is functional, on the capacity characteristics of the battery or Supercap, on the drops incurred across the Carrier board circuit protection elements, and on the operating temperature. In general terms, a suitable lithium battery solution can provide RTC backup current on a scale of years; the Supercap solution on a scale of days to weeks.

Figure 11 RTC Backup: Coin Battery / Super Cap

Coin Battery Holder, R/A, SMT

# 2.12 Reserved / Test Interfaces

The Module TEST# pin (pin S157) should normally be left not connected. If pulled low, then Module specific test function(s) may be enabled.

Reserved pins should be left not connected and may be used in future revisions of the SMARC specification.

# 3 DISPLAY INTERFACES

#### 3.1 Module LVDS

#### 3.1.1 NEC 1280 x 768 Single Channel LVDS Example

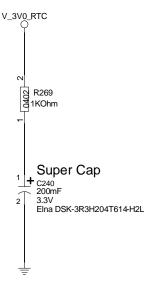

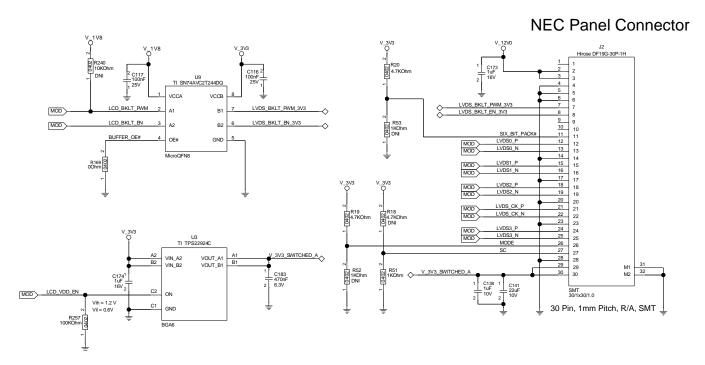

The Module LVDS interface may be used with single channel LVDS displays. SMARC Modules typically support LVDS 18 bit single channel operation (three data pairs plus one clock pair). They may also support LVDS 24 bit single channel operation (four data pairs plus one clock pair). Recall that there are two 24 bit color mappings in common use: most significant color bits on fourth data pair (sometimes referred to as the standard 24 bit mapping), and least significant color bits on the fourthLVDS data pair (referred to as 24 bit / 18 bit compatible or as 24 bit / 6 bit pack or similar). The standard 24 bit color mapping is more common but is incompatible with the 18 bit packing.

The example below shows an implementation used with an NEC 1280 x 768 single channel LVDS panel (NL 12876AC18-03). This panel uses a discrete wire 30 pin Hirose DF19 series connector. The panel backlight electronics accepts a 12V supply, and panel brightness is controlled by a 3.3V PWM signal. There is no EDID EEPROM on this particular NEC display.

This display happens to support 18 bit, 24 bit / 18 bit compatible and standard 24 bit LVDS packings. The panel also allows the image to be reversed. This can be useful if you find the panel connector orientations to be inconvenient – you can rotate the display 180 degrees, alter the scan direction strap, and have the image appear in the correct orientation. These options are set by pull-up and pull-down choices on connector pins 11, 26 and 27 in the image below. Refer to the display data sheet for further information.

The display LVDS data and clock differential pairs may be connected directly to the SMARC Module. The backlight PWM and panel enable need level translation and / or buffering as shown in the figure.

Figure 12 Module LVDS: NEC Single Channel Display

Power for the display's logic is gated by the Module LCD VDD EN signal, as shown above.

The NEC LVDS display in the example above accepts a 12V feed to power the display's LED backlight. The SMARC Module provides two backlight control signals, LCD\_BKLT\_EN and LCD\_BKLT\_PWM (enable and brightness).

Some displays require a higher voltage feed to their LED backlight electronics. An example of this is given in **Section 9.6 High Voltage LED Supply.**

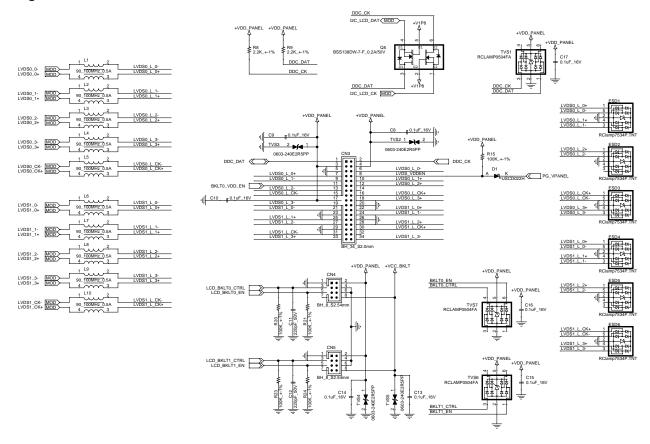

#### 3.1.2 LVDS Dual Channel example

The schematic example below shows an implementation on the Carrier that can be used either for a dual channel LVDS display or two single channels LVDS displays with common supply voltage. The LVDS signals are routed through common mode chokes to the LVDS connector. All display signals include ESD devices. Supply voltage for LVDS display and backlight can be selected by jumper settings. The control signals for backlight, LVDS display and I2C bus are routed over level shifters from 1.8V on SMARC connector side to the display I/O voltage.

Additional comments to schematic example:

Signal LVDS VDDEN:

If FET power switching is used this signal pin can also be connected to EN\_PANELPOWER instead of PG\_VPANEL. In this case PU resistor R15 and diode D1 can be removed.

LVDS connector type:

Neither connector type nor pinout of the connector underlies any standards specification. So everyone is free to select a suitable LVDS connector for best application fit.

Comment on jumper settings:

CN1-JP1:

Default: JP1 shorting 1-2 => Panel supply = 3.3V Alternate: JP1 shorting 5-6 => Panel supply = 5.0V

CN2-JP2:

Default: JP2 shorting 3-4 => Backlight voltage = 12.0V Alternate: JP2 shorting 5-6 => Backlight voltage = 5.0V

Comment on alternate power switching:

If leakage currents are not considered as an issue for the design, the load switch might be replaced by a P-Channel FET and N-Channel FET for the Gate control.

- Comment on different power rails for both LVDS channels:

It might be considered to implement different voltage rails for both channels, which is not covered with this design example.

- Comment on ESD-Devices:

Place the ESD device close to the LVDS connector and close to the backlight pin header.

In a LVDS implementation with two single LVDS channels, the panel EDID EEPROMs would be in conflict and measures need to be taken to avoid this. One possible solution is that the second LVDS EDID EEPROM could be read over the I2C\_GP pin pair rather than the I2C\_LCD pin pair.

Figure 13 LVDS Dual Channel

Figure 14 LVDS Dual Channel Power Supply

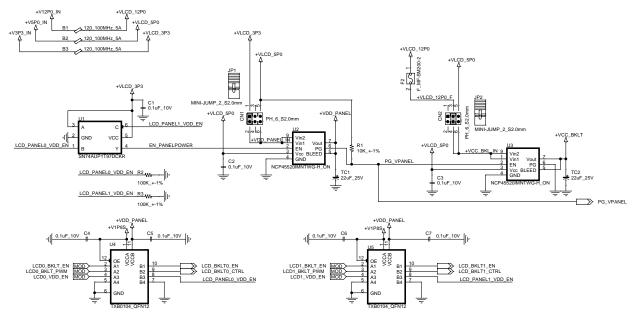

## 3.1.3 Display Parameters and EDID

Flat panel display parameters (horizontal resolution, vertical resolution, pixel clock rate, blanking periods, etc.) may be hard-coded into a boot-loader or they may be read by boot-loader code from an industry standard data structure known as EDID (Extended Display Identification Data). EDID data is stored in an EEPROM accessed via I2C. The EDID EEPROM may reside on the display assembly or elsewhere in the path between the SOC and the display – on the Carrier or on a display adapter assembly.

If the EDID EEPROM resides on the display, then the cabled interface to the display must include the SMARC Module I2C\_LCD interface. The interface should be level translated and possibly buffered. The I2C voltage levels on the display are most likely to be at 3.3V levels. A set of back-to-back FETs may be used for I2C level translation, as shown in the figure immediately below. Alternatively, a device such as the Fairchild FXMA2102 I2C buffer / level translator may be used. There is a circuit example using the FXMA2102 later in this document.

In the display interface example above, with the 30 pin Hirose DF19 series connector, pins 9 and 10 could be used for the buffered I2C\_LCD clock and data, respectively.

The figure below shows an EDID EEPROM implementation that may be used on a Carrier. It might be advantageous to use a socket for the EEPROM to allow display parameters to be swapped out. Alternatively, system software could update the EEPROM if the EEPROM WP (Write Protect) pin is set to enable writes. Or, the system designer could implement an EEPROM programming header for update purposes.

Caution: if there is an EDID EEPROM on the Carrier and on the display, there will be an I2C address conflict unless one of the two is disabled or set to an alternate address. VESA EDID EEPROMs are expected at 7 bit I2C address 0x50.

There are many EDID editors available, some for free. It can be very useful to have access to one if you are trying to adapt a new panel, and if your SMARC Module software knows what to do with EDID data. Alternatively, your SMARC Module and / or Carrier board vendor may well be able to help with display adaptations.

Figure 15 Carrier EDID EEPROM

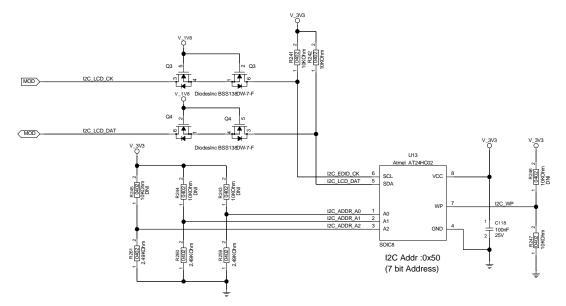

#### **3.2 HDMI**

Note: a license may be needed to market HDMI capable products. Check with the HDMI organization (www.hdmi.org) and with your SMARC Module vendor.

The SMARC HDMI data pairs may be routed directly from the SMARC Module pins to a suitable Carrier HDMI connector. Since HDMI is a hot-plug capable interface, it is important for the Carrier to implement ESD protection on all of the HDMI lines. The ESD protection on the data lines must be low capacitance so as not to degrade high speed signaling. The data lines must route through the ESD protection device pins in a no-stub fashion. The ESD protection should be located close to the HDMI connector.

The SMARC pins HDMI\_CTRL\_CK and HDMI\_CTRL\_DAT require level translation from V\_1V8 to the 5V levels that HDMI uses on those pins. These lines also require pull-up resistors to V\_1V8 (the pull-ups are not included on the SMARC Module, because integrated HDMI protection devices such as the Texas Instruments TPD12S016 include the pull-ups in their parts). And, finally, 5V power switching / current limiting to the HDMI connector is required on the Carrier.

The ESD protection, level translation and power switching / limiting are all dealt with in integrated devices such as the TI TPD12S016. A circuit diagram is shown in the following figure. The TPD12S016 must be placed close to the HDMI connector, and the HDMI data traces routed in daisy chain fashion (and as differential pairs) from the SMARC Module pins, to and through the TPD12S016 pins, and on to the HDMI connector pins. The TPD12S016 pin-out is specifically designed to facilitate this.

Figure 16 HDMI Implementation

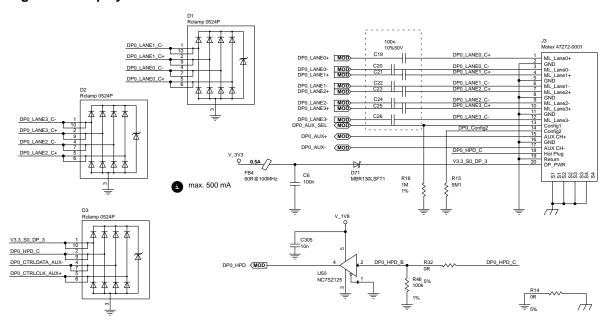

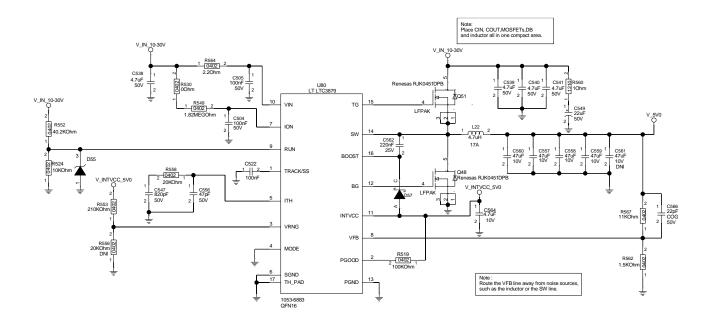

# 3.3 DisplayPort (DP++)

DisplayPort is directly supported by a dual-source DDI. ESD protection, DC blocking capacitors and hot plug detect are the only components required.

The DisplayPort differential data pairs (Lane [0..3]) are AC coupled off Module with capacitors C19-C26. Place the AC blocking capacitors close to the DisplayPort connector. The Aux differential pair is AC coupled on the Module. ESD clamping diodes D1, D2 and D3 protect the Module from external ESD events and should be placed near the DisplayPort connector. The pin-out of the ESD clamp diodes allows for a trace to run under the chip connector to two pins.

The Carrier provides up to 500 mA of 3.3V power to the DisplayPort connector. Diode D71 prevents back feeding of power in the event that the monitor is powered up when the Carrier is powered down. Config lines 1 and 2 are pulled to ground per the VESA specification.

The DisplayPort Hot Plug Detect signal is buffered by U50 which prevents back feeding of power from the display to the Module as well as level translation to 3.3V levels.

R14 connect logic and chassis ground together. Other techniques may be used depending on the overall grounding strategy.

Note: The reference schematics assume that the Module's DisplayPort is dual-source capable – dual source indicates that the Module can output DisplayPort or HDMI/DVI based on the DDC\_AUX\_SEL signal.

Figure 17 DisplayPort ++

#### 3.3.1 HDMI over DP++

A Dual-mode source Module requires level shifters on the Carrier to convert the low-swing AC coupled differential pairs from the video source to HDMI compliant current mode differential outputs. The example schematics use a Chrontel CH7318C translator which supports data rates up to 1.65GB/s per lane. FET based passive level translators can be used for lower data rates.

The DisplayPort AUX channel is configured as a DDC interface for HDMI. Further information on preemphasis as well as output current trim capabilities of the CH7318C can be found in the Chrontel datasheet.

ESD clamping diodes D159, D160 and D161 protect the Module from external ESD events and should be placed near the HDMI connector. The pin-out of the ESD clamp diodes allows for a trace to run under the chip connector to two pins.

HDMI uses I2C signaling for the DDC. Resistors R1319 and R1322 provide the necessary pull-up. The FET U35 provides the Hot Plug Detect signal

The Carrier provides 5V power to the HDMI connector. A series diode (D72) should be used to prevent back feeding of power in the event that the monitor is powered up when the Carrier is powered down. The HDMI Hot Plug Detect signal is buffered by two FETs U32 and U33 which prevent back feeding of power from the display to the Module as well as level translation to 3.3V levels.

Note: The reference schematics assumes that the Module's DDI ports are dual-source capable – dual source indicates that the Module can output DisplayPort or HDMI/DVI based on the DDC\_AUX\_SEL signal.

Figure 18 HDMI over DP++

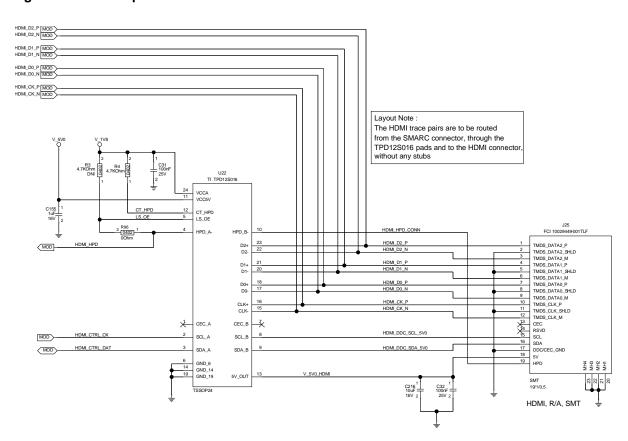

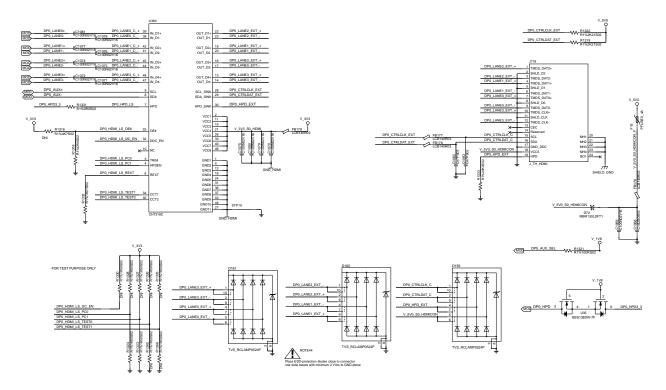

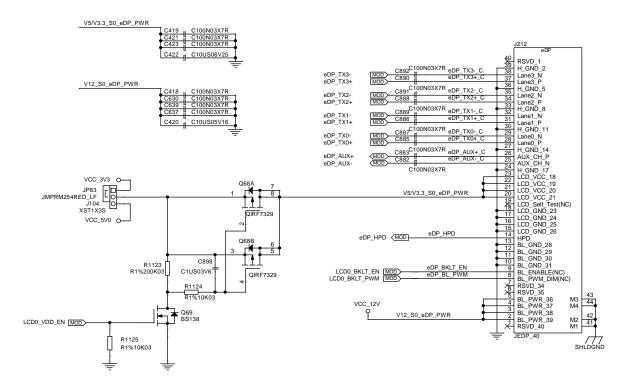

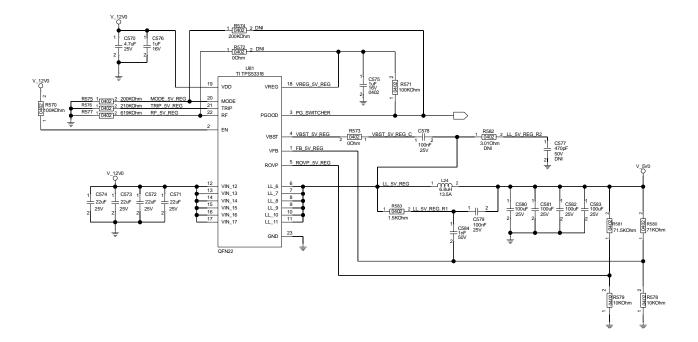

## 3.4 Embedded DisplayPort (eDP)

The reference schematic provides a generic eDP interface. The eDP connector used in the design is an example only. Other connectors can be used based on the design requirements. JP83 selects 3.3 or 5V for the panel power. R1125 ensures that panel power is disabled when the Module is powering up and before the signal is actively driven. The panel control signals eDP\_BKLT\_EN, eDP\_BKLT\_CTRL as well as eDP\_HPD are 3.3V level signals, check your panel specifications for correct voltage levels and provide translation if necessary. The reference design supports individual backlight control signals. It should be noted that some panels handle these functions over the AUX channel.

The traces from JP83 and associated FETs to the eDP connector carry power to the panel. The traces should be routed with appropriate thickness to handle the current expected. eDP\_TX and eDP\_AUX differential pairs should be routed as high speed differential pairs. The panel control signals are low speed and do not require any additional care.

Figure 19 Embedded DisplayPort (eDP)

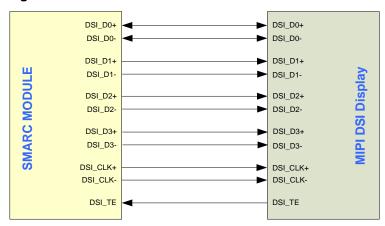

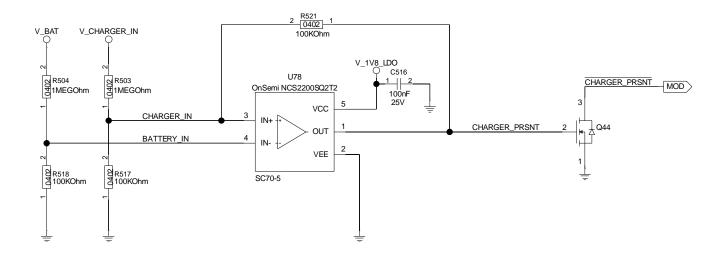

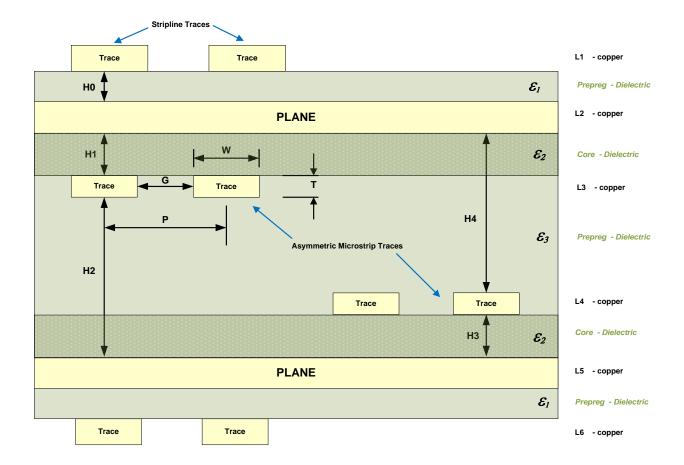

#### 3.5 MIPI DSI