# Smart Mobility ARChitecture

# **Hardware Specification**

Version 2.0 June 2<sup>nd</sup>, 2016

### 1 Introduction

### 1.1 Legal

© Copyright 2016, SGET Standardization Group for Embedded Technology e.V.

Note that some content of this SGET document may be legally protected by patent rights not held by SGET. SGET is not obligated to identify the parts of this specification that require licensing or other legitimization. The contents of this SGET document are advisory only. Users of SGET documents are responsible for protecting themselves against liability for infringement of patents. All content and information within this document are subject to change without prior notice.

SGET provides no warranty with regard to this SGET document or any other information contained herein and hereby expressly disclaims any implied warranties of merchantability or fitness for any particular purpose with regard to any of the foregoing. SGET assumes no liability for any damages incurred directly or indirectly from any technical or typographical errors or omissions contained herein or for discrepancies between the product and this SGET document. In no event shall SGET be liable for any incidental, consequential, special, or exemplary damages, whether based on tort, contract or otherwise, arising out of or in connection with this SGET document or any other information contained herein or the use thereof.

### 1.2 Revision History

| Rev | Date          | Originator | Notes                                                                     |

|-----|---------------|------------|---------------------------------------------------------------------------|

| 1.0 | Dec. 20, 2012 | S. Milnor  | Initial release                                                           |

| 1.1 | May 29, 2014  | S. Milnor  | Change notes for V1.0 to V1.1 can be found in the V1.1 document           |

| 2.0 |               | C. Eder    | See section 10.1 'SMARC HW Specification Changes V1.1 to V2.0' on page 72 |

# 1.3 Table of Contents

| 1 lı | ntro  | duction                                                   | 2        |

|------|-------|-----------------------------------------------------------|----------|

| 1    | .1    | Legal                                                     | 2        |

| 1    | .2    | Revision History                                          | 2        |

| 1    | .3    | Table of Contents                                         |          |

| 1    | .4    | Table of Figures                                          |          |

| 1    | .5    | General Introduction                                      |          |

| 1    | .6    | Purpose of This Document                                  |          |

| 1    | .7    | Document and Standards References                         |          |

| 2 N  | /lodu | ule Overview                                              | 9        |

|      | 2.1   | Form Factor Feature Summary                               |          |

| 2    | 2.2   | Module Interface Summary                                  |          |

| 3 N  | /lodu | ule Interface Required and Optional Features              | 12       |

|      | 3.1   | Required and Optional Feature Table                       |          |

| 3    | 3.2   | Feature Fill Order                                        |          |

| 4 S  | Siana | al Descriptions                                           | 15       |

|      | .1    | Signal Direction and Type Definitions                     |          |

|      | .2    | Internal Display Interfaces                               |          |

|      |       | 4.2.1 Primary LCD Display Support Signals                 |          |

|      |       | 4.2.2 Primary Display – 18 / 24 Bit LVDS LCD Dual Channel | 17       |

|      |       | 4.2.3 LVDS / eDP Pin Sharing                              | 18       |

|      |       | 4.2.4 LVDS / DSI Pin Sharing                              | 19       |

|      |       | 4.2.5 Secondary (HDMI) Display                            | 20<br>21 |

|      |       | 4.2.7 DP++                                                |          |

| 4    | .3    | Camera Interfaces                                         |          |

| 7    |       | 4.3.1 Camera Configurations                               |          |

|      |       | 4.3.2 Camera Power Enables and Resets                     | 23       |

|      |       | 4.3.3 Camera I2C Support                                  | 23       |

|      |       | 4.3.4 MIPI CSI Configuration CSI-2 and CSI-3              | 24       |

|      |       | 4.3.5 Serial Cameras In                                   |          |

| _    | .4    | SDIO Card (4 bit) Interface                               |          |

| 4    | .5    | SPI Interfaces                                            | 26       |

|      |       | 4.5.1 SPI0                                                | 26       |

| 1    | .6    |                                                           |          |

| 4    | 0     | Audio                                                     |          |

|      |       | 4.6.2 HDA / I2S                                           | 27       |

| 4    | .7    | I2C Interfaces                                            |          |

| 4    | .8    | Asynchronous Serial Ports                                 |          |

| 4    | .9    | CAN Bus                                                   |          |

| 4    | .10   | USB Interfaces                                            | 30       |

|      |       | 4.10.1USB Signal Assignments                              | 30       |

|      |       | 4.10.2USB Signals                                         | 30       |

|      |       | 4.10.3USB[0:5]_EN_OC# Discussion                          |          |

| 4    | .11   | PCI Express                                               | 32       |

|   |             | 4.11.1PCI Express Link Width                                                                         | 32  |

|---|-------------|------------------------------------------------------------------------------------------------------|-----|

|   | 4.12        |                                                                                                      | 33  |

|   | 4.13        | Ethernet                                                                                             | 34  |

|   | 4.14        | Watchdog                                                                                             | 35  |

|   | 4.15        | GPIO                                                                                                 | 36  |

|   | 4.16        | Management Pins                                                                                      | 37  |

|   | 4.17        | Boot Select                                                                                          | 38  |

|   | 4.18        | IO Levels                                                                                            | 39  |

|   |             | 4.18.1 Default I/O 1.8V                                                                              | 39  |

|   |             | 4.18.2Signals at 3.3V                                                                                |     |

|   | <i>1</i> 10 | Power and GND                                                                                        |     |

|   |             | JTAG                                                                                                 |     |

|   |             | Module Terminations                                                                                  |     |

|   | 4.21        | 4.21.1 Module Input Terminations - General                                                           |     |

|   |             | 4.21.2Module Terminations – Specific Recommendations                                                 |     |

|   | 4.22        | Carrier / Off-Module Terminations                                                                    | 43  |

| _ |             | de Pire Cort Mari                                                                                    |     |

| 5 |             | Ile Pin-Out Map                                                                                      |     |

|   | 5.1         | Module Pin-Out                                                                                       | 44  |

| 6 | Mech        | anical Definitions                                                                                   | 49  |

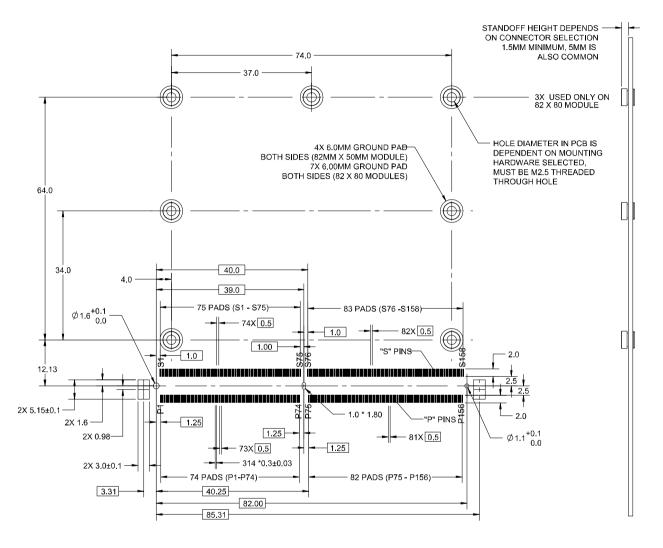

|   | 6.1         | Carrier Connector                                                                                    |     |

|   | 6.2         | Module and Carrier Connector Pin Numbering Convention                                                |     |

|   | 6.3         | Module Outline – 82mm x 50mm Module                                                                  |     |

|   | 6.4         | Module Outline – 82mm x 80mm Module                                                                  |     |

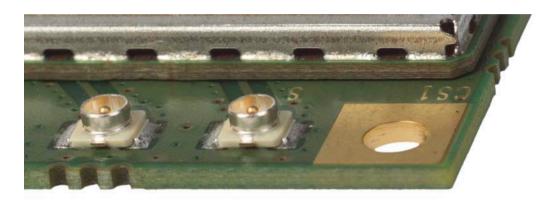

|   |             | 6.4.1 RF Connector Placement                                                                         | 54  |

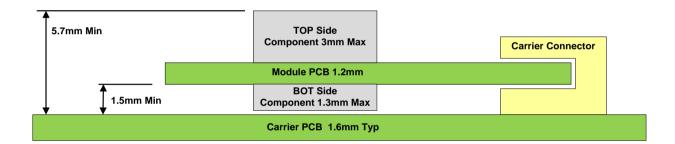

|   | 6.5         | Module 'Z' Height Considerations                                                                     | 56  |

|   | 6.6         | Carrier Board Connector PCB Footprint                                                                | 57  |

|   | 6.7         | Module and Carrier Board Mounting Holes – GND Connection                                             | 58  |

|   | 6.8         | Carrier Board Standoffs                                                                              | 58  |

|   | 6.9         | Thermal Attachment Points                                                                            | 58  |

|   | 6.10        | Heat Spreader – 82mm x 50mm Module                                                                   | 59  |

|   | 6.11        | Heat Spreader – 82mm x 80mm Module                                                                   | 62  |

| 7 | Modi        | ıle Power                                                                                            | 63  |

| • | 7.1         | Input Voltage / Main Power Rail                                                                      |     |

|   | 7.2         | No Separate Standby Voltage                                                                          |     |

|   | 7.3         | RTC Voltage Rail                                                                                     |     |

|   | 7.4         | Power Sequencing                                                                                     |     |

|   |             | 7.4.1 x86 Power Management                                                                           |     |

|   | 7.5         | System Power Domains                                                                                 |     |

| 8 | MOD         | ULE AND CARRIER SERIAL EEPROMS                                                                       | 67  |

| 9 | Appe        | ndix A: LVDS LCD Color Mappings                                                                      | 68  |

|   | 9.1         | LVDS LCD Color Mappings                                                                              |     |

|   |             | 9.1.1 Single Channel LVDS LCD Color Mappings – General Information                                   | 69  |

|   |             | <ul> <li>9.1.2 Single Channel LVDS LCD 24 Bit Standard Color Mapping – Carrier Connections</li></ul> |     |

|   |             | 3.1.3 Duai Channel Lydd Lod 24 dil Sianuaiu Coloi Mapping — Camel Connections                        | / 1 |

| 10 Appendix C: Document Changes                                 | 72 |

|-----------------------------------------------------------------|----|

| 10.1 SMARC HW Specification Changes V1.1 to V2.0                | 72 |

| 10.1.1Pinout Comparison                                         |    |

| 1.4 Table of Figures                                            |    |

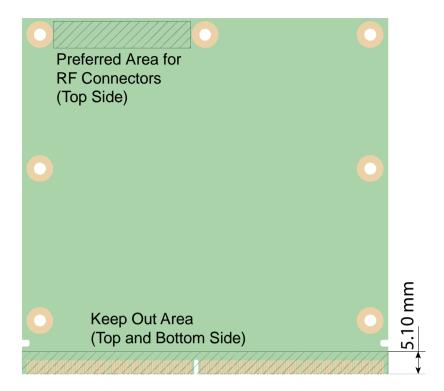

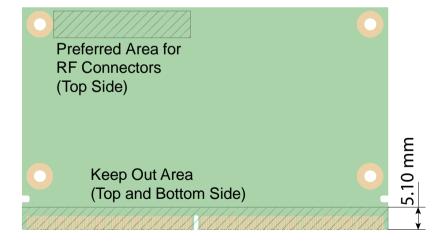

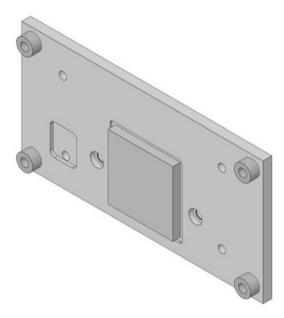

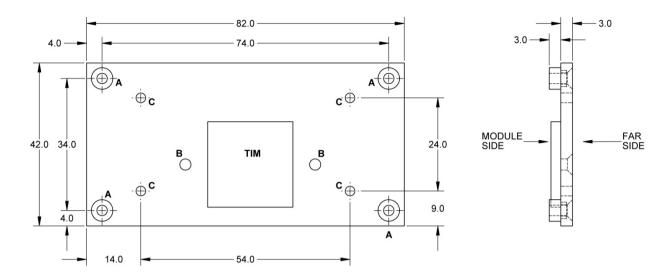

| Figure 1: 82mm x 50mm Module Outline                            | 51 |

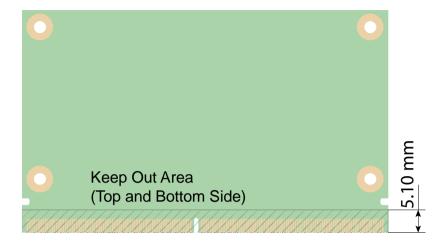

| Figure 2: Module Edge Finger Keep Out Area (82mm x 50mm Module) | 52 |

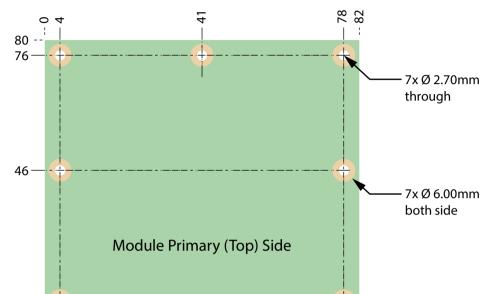

| Figure 3: 82mm x 80mm Module Outline                            | 53 |

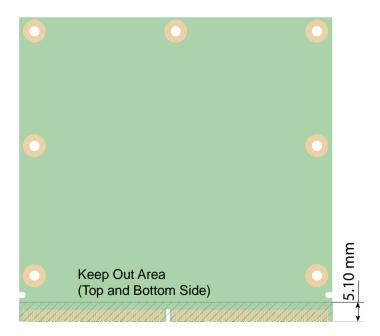

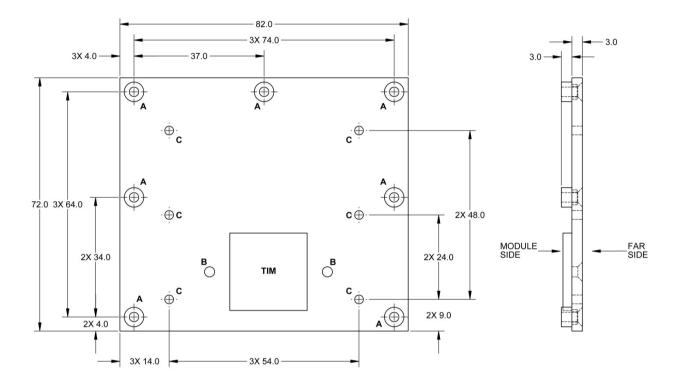

| Figure 4: Module Edge Finger Keep Out Area (82mm x 80mm Module) | 53 |

| Figure 5: u.FL connector                                        | 54 |

| Figure 6: RF connector placement (82mm x 80mm Module)           | 55 |

| Figure 7: RF connector placement (82mm x 50mm Module)           | 55 |

| Figure 8: Module Minimum 'Z' Height                             | 56 |

| Figure 9: Carrier Board Connector PCB Footprint                 | 57 |

| Figure 10: Heat Spreader Isometric View                         | 59 |

| Figure 11: Heat Spreader Plan View                              | 60 |

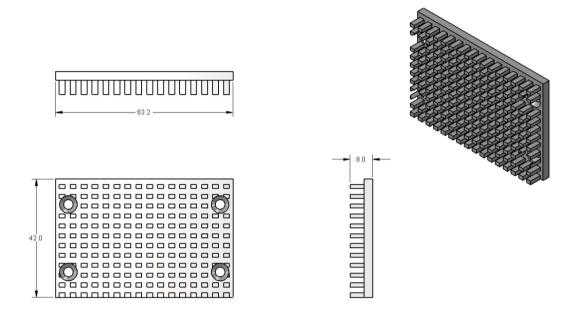

| Figure 12: Heat Sink Attachment Option                          | 61 |

| Figure 13: Heat Spreader - 82mm x 80mm Module                   | 62 |

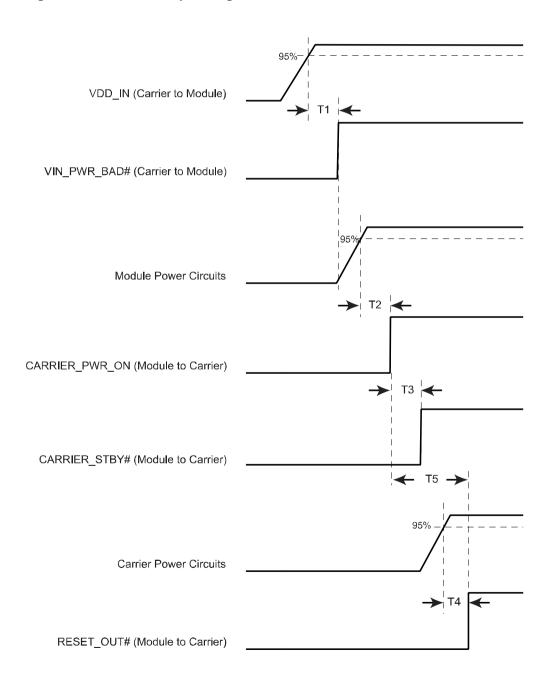

| Figure 14: Power On Sequencing                                  | 64 |

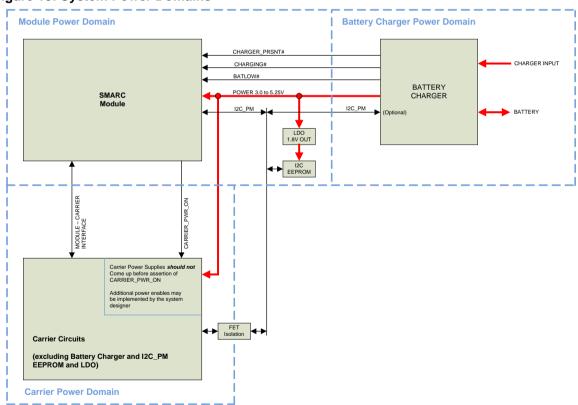

| Figure 15: System Power Domains                                 | 66 |

### 1.5 General Introduction

The SMARC ("Smart Mobility ARChitecture") is a versatile small form factor computer Module definition targeting applications that require low power, low costs, and high performance. The Modules will typically use ARM SOCs similar or the same as those used in many familiar devices such as tablet computers and smart phones. Alternative low power SOCs and CPUs, such as tablet oriented X86 devices and other RISC CPUs *may* be used as well. The Module power envelope is typically under 6W although designs up to about 15W are possible.

Two Module sizes are defined: 82mm x 50mm and 82mm x 80mm. The Module PCBs have 314 edge fingers that mate with a low profile 314 pin 0.5mm pitch right angle connector (the connector is sometimes identified as a 321 pin connector, but 7 pins are lost to the key).

The Modules are used as building blocks for portable and stationary embedded systems. The core CPU and support circuits, including DRAM, boot flash, power sequencing, CPU power supplies, GBE and dual channel LVDS display transmitter are concentrated on the Module. The Modules are used with application specific Carrier Boards that implement other features such as audio CODECs, touch controllers, wireless devices, etc. The modular approach allows scalability, fast time to market and upgradability while still maintaining low costs, low power and small physical size.

### 1.6 Purpose of This Document

This document defines the Module mechanical, electrical, signal and thermal parameters at a level of detail sufficient to provide a framework for SMARC Module and Carrier Board designs.

### 1.7 Document and Standards References

- BT.656 ("Recommendation ITU-R BT.656-5 Interface for digital component video signals in 525-line and 625-line television systems operating at the 4:2:2 level of Recommendation ITU-R BT.601"), International Telecommunications Union, December 2007 (www.itu.int)

- CAN ("Controller Area Network") Bus Standards ISO 11898, ISO 11992, SAE J2411

- CSI-2 (Camera Serial Interface version 2) The CSI-2 standard is owned and maintained by the MIPI Alliance ("Mobile Industry Processor Alliance") (www.mipi.org)

- CSI-3 (Camera Serial Interface version 3) The CSI-2 standard is owned and maintained by the MIPI Alliance ("Mobile Industry Processor Alliance") (www.mipi.org)

- COM Express the formal title for the COM Express specification is "PICMG<sup>®</sup> COM.0 COM Express Module Base Specification", Revision 2.1, May 14, 2012. This standard is owned and maintained by the PICMG ("PCI Industrial Computer Manufacturer's Group") (www.picmg.org)

- DisplayPort and Embedded DisplayPort These standards are owned and maintained by VESA ("Video Electronics Standards Association") (www.vesa.org)

- D-PHY CSI-2 physical layer standard owned and maintained by the MIPI Alliance (www.mipi.org)

- DSI (Display Serial Interface) The DSI standard is owned and maintained by the MIPI Alliance ("Mobile Industry Processor Alliance") (www.mipi.org)

- **eMMC** ("Embedded Multi-Media Card") The eMMC electrical standard is defined by JEDEC JESD84-B45 and the mechanical standard by JESD84-C44 (www.jedec.org)

- **eSPI** ("Enhanced Serial Peripheral Interface") The eSPI Interface Base Specification is defined by Intel (https://downloadcenter.intel.com/de/download/22112)

- Fieldbus this term refers to a number of network protocols used for real time industrial control. Refer to the following web sites: www.profibus.com/downloads and www.canopen.org

- GBE MDI ("Gigabit Ethernet Medium Dependent Interface") This is defined by IEEE 802.3. The 1000Base-T operation over copper twisted pair cabling is defined by IEEE 802.3ab (www.ieee.org)

- HDA (HD Audio), High Definition Audio Specification, Intel, Revision 1.0a, June 17, 2010 (http://www.intel.com/content/dam/www/public/us/en/documents/product-specifications/high-definition-audio-specification.pdf)

- HDMI Specification, Version 1.3a, November 10, 2006 © 2006 Hitachi and other companies (www.hdmi.org)

- I2C Specification, Version 2.1, January 2000, Philips Semiconductor (now NXP) (www.nxp.com)

- I2S Bus Specification, Feb. 1986 and Revised June 5, 1996, Philips Semiconductor (now NXP)

- IEEE1588 2008. IEEE Standard for a Precision Clock Synchronization Protocol for Networked Measurement and Control Systems (http://standards.ieee.org/findstds/standard/1588-2008.html)

- **JTAG** ("Joint Test Action Group") This is defined by IEEE 1149.1-2001 IEEE Standard Test Access Port and Boundary Scan Architecture (www.ieee.org)

- MXM3 Graphics Module Mobile PCI Express Module Electromechanical Specification, Version 3.0, Revision 1.1, © 2009 NVidia Corporation (www.mxm-sig.org)

- PICMG® EEEP Embedded EEPROM Specification, Rev. 1.0, August 2010 (www.picmg.org)

- PCI Express Specifications (www.pci-sig.org)

- Serial ATA Revision 3.1, July 18, 2011, Gold Revision, © Serial ATA International Organization (www.sata-io.org)

- SD Specifications Part 1 Physical Layer Simplified Specification, Version 3.01, May 18, 2010, © 2010 SD Group and SD Card Association ("Secure Digital") (www.sdcard.org)

- **SM Bus** "System Management Bus" Specification Version 3.0, 2© 2014 System Management Interface Forum, Inc. (http://www.smbus.org)

- SPI Bus "Serial Peripheral Interface" de-facto serial interface standard defined by Motorola. A good description may be found on Wikipedia

(http://en.wikipedia.org/wiki/Serial\_Peripheral\_Interface\_Bus)

- USB Specifications (www.usb.org)

### 2 MODULE OVERVIEW

### 2.1 Form Factor Feature Summary

- Small form factor, low profile and low power edge-finger card format Module with pin-out optimized for ARM and x86 architecture processors; may also be used with low power, tablet oriented X86 and RISC devices.

- Two Module sizes:

- o 82mm x 50mm

- 82mm x 80mm

- Carrier Board connector: 314 pin 0.5mm pitch R/A memory socket style connector

- Originally defined for use with MXM3 graphics cards

- o SMARC Module pin-out is separate from and not related to MXM3 pin-out

- o Multiple sources for Carrier Board connector

- Low cost

- o Low profile:

- As low as 1.5mm (Carrier Board top to Module bottom)

- Other stack height options available, including 2.7mm, 5mm, 8mm

- Overall assembly height (Carrier Board top to tallest Module component) is less than 6mm

- Excellent signal integrity suitable for 2.5 GHz / 5 GHz / 8 GHz data rate signals such as PCle Gen 1, Gen 2 and Gen 3.

- Robust, vibration resistant connector

- Module input voltage range: 3.0V to 5.25V

- o Allows operation from 3.6V nominal Lithium-ion battery packs

- Allows operation from 3.3V fixed DC supply

- Allows operation from 5.0V fixed DC supply

- Single supply (no separate standby voltage)

- o Module power pins allow 5A max, or 15W max input power at 3.0V

- Low power designs

- 2 to 6W typical Module power draw during active operation

- Fanless

- Passive cooling

- o Low standby power

- Design for battery operation

- 1.8V default I/O voltage

### 2.2 Module Interface Summary

The interfaces listed below are available per the Module pin definition. Some features are optional and availability is Module design dependent.

- Display Interfaces

- Single or dual channel LVDS LCD 18 or 24 bit (usually derived from SOC parallel LCD data)

- Panel support signals (I2C, Power Enables, PWM)

- Support for dual channel implementations

- Multiplexing with eDP and MIPI DSI

- o HDMI port multiplexed with DP++ full featured implementation

- o Additional full featured DisplayPort++

- Camera Interfaces

- Serial configuration: MIPI CSI (2 lane) + MIPI CSI (2 or 4 lane)

- SDIO Interface

- 4 bit SDIO card interface with support lines

- SPI Interfaces

- Two SPI interfaces

- One maybe implemented as eSPI (x86) or QSPI (ARM)

- Audio Interfaces

- One I2S interface

- One HDA interfaced multiplexed with second I2S interface

•

- I2C Interfaces

- Five I2C interfaces

- Power Management

- General Purpose

- Camera 2 interfaces

- LCD Display ID

- HDMI interface also has private I2C interface for HDMI use

- Asynchronous Serial Port Interfaces

- Four asynchronous serial ports

- Two with 2 wire handshake (RXD, TXD, RTS#, CTS#)

- Two with data only (RXD, TXD)

- Logic level interface

- CAN Bus Interfaces

- Two CAN bus interfaces

- Logic level signals from Module based CAN bus protocol controllers

- RXD, TXD only

- USB Interfaces

- Six ports total

- Two sets of super speed signals for support of two USB 3.0 ports

- Two ports allows USB OTG (USB client or host)

- USB support signals (VBUS enable / Over-current detects, OTG support signals)

- PCI Express

- Four PCle lanes

- o PCIe Gen1, Gen 2 or Gen 3 (Module dependent)

- Three reference clock pairs

- Three PCIe reset signals

- Common PCIe wake signal (PCIE\_WAKE#)

- SATA Interface

- o One SATA interface

- o Gen 1, 2 or 3 (Module dependent)

- Gigabit Ethernet

- Two analog GBE MDI interface

- No magnetics on Module

- o LED support signals

- CTREF (center tap reference voltage) for Carrier magnetics (if required by the Module GBE PHY)

- Individual IEEE1588 trigger signal for each Ethernet interface to allow for enhanced real time applications. This utilizes a software definable pin (SDP) from the Ethernet controller.

- Watchdog Timer Interface

- General Purpose I/O

- Twelve GPIO signals

- Specific alternate functions are assigned to some GPIOs

- PWM / Tachometer capability

- Camera support

- HD Audio reset

- System and Power Management Signals

- Reset out and Reset in

- Power button in

- o Power source status

- Module power state status

- System management pins

- Battery and battery charger management pins

- Carrier Power On control

- Boot Source Select

- Three pins to allow selection from Carrier Board

- Select options to include boot from one of the following:

- Module SPI

- Module eMMC Flash

- Module NAND / NOR Flash (vendor defined)

- Module Remote Boot (Network or Serial Port, vendor defined)

- Carrier SPI

- Carrier SD Card

- Carrier SATA

- JTAG functions for CPU debug and test are optionally implemented on separate small form factor connector(s)

# 3 MODULE INTERFACE REQUIRED AND OPTIONAL FEATURES

# 3.1 Required and Optional Feature Table

Required and optional features for an SMARC Module are summarized in the table below.

"Shall" indicates a mandatory requirement

"Should" indicates a recommended but not mandatory requirement

"May" indicates a lesser used optional interface

"Alternate" indicates an optional interface, implemented on pins shared with another use

| Feature            | Sub Feature                                | Requirement | Notes                         |

|--------------------|--------------------------------------------|-------------|-------------------------------|

|                    |                                            |             |                               |

| LVDS LCD           | 18 bit single channel                      | Should      | Default Display (serial LVDS) |

|                    | 24 bit single channel – 18 bit compatible  | Should      |                               |

|                    | 24 bit single channel – standard color map | May         |                               |

|                    | 24 bit dual channel – 18 bit compatible    | May         |                               |

|                    | 24 bit dual channel – standard color map   | Мау         |                               |

| HDMI               | HDMI display interface                     | Should      |                               |

| DP on HDMI<br>Pins |                                            | Мау         |                               |

| DP++               | DisplayPort++                              | Мау         |                               |

| Camera             | CSI0 - 2 lane                              | Should      |                               |

|                    | CSI1 – 2 lane implementation               | May         |                               |

|                    | CSI1 – 4 lane implementation               | Мау         |                               |

| SDIO               | SDIO (4 bit, for SD cards)                 | Should      | May be Carrier boot device    |

| SPI                | SPI0                                       | Should      | May be Carrier boot device    |

|                    | eSPI                                       | Should      | May be Carrier boot device    |

| Audio              | 12\$0                                      | Should      |                               |

|                    | HDA                                        | Should      |                               |

| I2C                | Power Management                           | Shall       |                               |

|                    | General Purpose                            | Shall       |                               |

|                    | Camera                                     | Should      |                               |

|                    | LCD Display I/D                            | Should      |                               |

| Serial Ports | SER0 (4 wire)                               | Shall               |                                                            |

|--------------|---------------------------------------------|---------------------|------------------------------------------------------------|

|              | SER1 (2 wire)                               | Shall               |                                                            |

|              | SER2 (4 wire)                               | Should              |                                                            |

|              | SER3 (2 wire)                               | Should              |                                                            |

|              |                                             |                     |                                                            |

| CAN Bus      | CAN0                                        | May                 |                                                            |

|              | CAN1                                        | May                 |                                                            |

| USB          | USB0 - as USB 2.0 Client                    | Should              |                                                            |

| 002          | USB0 – as OTG                               | May                 | USB0 <i>shall</i> be                                       |

|              | USB0 - as USB 2.0 Host                      | May                 | implemented                                                |

|              | USB1 – as USB 2.0 Host                      | Shall               |                                                            |

|              | USB[2:5] - as USB 2.0 Host                  | May                 |                                                            |

|              | USBss[2:3]                                  | May                 | Fill order: first #2 then #3                               |

|              | USB3 - as USB 3.0 Client / OTG              | May                 | Tim Gradi. mot w2 thom we                                  |

|              | GODG AC COD C.O CHOIR / GTG                 | , may               |                                                            |

| PCle         | PCIE_A (x1 Gen 1 Root)                      | Should              |                                                            |

|              | PCIE_B (x1 Gen 1 Root)                      | May                 |                                                            |

|              | PCIE_C (x1 Gen 1 Root)                      | May                 |                                                            |

|              | PCIE_D (x1 Gen 1 Root)                      | May                 |                                                            |

|              | PCIE_ Target operation                      | May                 |                                                            |

|              | PCIE Gen 2 and Gen 3 operation              | May                 |                                                            |

|              |                                             |                     |                                                            |

| SATA         | SATA Gen 1                                  | Should              | May be Carrier boot device                                 |

|              | SATA Gen 2 operation                        | May                 |                                                            |

|              | SATA Gen 3 operation                        | May                 |                                                            |

| GBE          | GBE0                                        | Should              |                                                            |

| <u> </u>     | GBE1                                        | May                 |                                                            |

|              | IEEE 1588 Trigger Signals<br>(GBE[0:1]_SDP) | May                 |                                                            |

|              |                                             |                     |                                                            |

| Watchdog     | WDT Out                                     | Should              |                                                            |

| GPIO         | GPIOs – 12x                                 | Shall               |                                                            |

|              | GPIO interrupt capability – 12x             | Shall               |                                                            |

|              | GPIO Camera Support                         | Shall<br>(see Note) | As appropriate for Module Camera implementation            |

|              | GPIO5 PWM capability                        | Should              |                                                            |

|              | GPIO6 Tachin capability                     | Should              |                                                            |

| Management   | System and power management features        | Shall               | See section 7.4.1 'x86<br>Power Management' for<br>details |

| Boot Select |                          | Shall  |                                       |

|-------------|--------------------------|--------|---------------------------------------|

|             |                          |        |                                       |

| Force Recov |                          | Should | See section 4.17 for details          |

|             |                          |        |                                       |

| JTAG        | JTAG connector on Module | May    | Some vendors prefer test point access |

| RTC         |                          | Should |                                       |

### 3.2 Feature Fill Order

Features **shall** be filled in a low – to – high order, based on the signal group names. For example, there are six possible USB ports, designated with signal prefixes USB0 to USB5. If a Module design implements only two USB, those would be USB0 and USB1. The PCIe links are designated PCIE\_A, PCIE\_B, PCIE\_C and PCIE\_D. If only one is implemented, it would be PCIE\_A.

USB 3.0 port number 2 is the first in the fill order as the counting of USB 3.0 lines starts with number 2. USB Super Speed operation is only defined for SMARC USB ports USB2 and USB3. Therefore USB2 is the first in the fill order for USB Super Speed (aka USB 3.0) implementations on SMARC.

# 4 SIGNAL DESCRIPTIONS

# 4.1 Signal Direction and Type Definitions

| Direction | Type / Tolerance    | Notes                                                                                                                                                                                                              |

|-----------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input     |                     | Input to the Module                                                                                                                                                                                                |

| Output    |                     | Output from the Module                                                                                                                                                                                             |

| Output OD |                     | Open drain output from the Module                                                                                                                                                                                  |

| Bi-Dir    |                     | Bi-directional signal (can be input or output)                                                                                                                                                                     |

| Bi-Dir OD |                     | Bi-directional signal; output from the Module is open drain                                                                                                                                                        |

|           | VDD_IN              | Signal <i>may</i> be exposed to Module input voltage range (3.0 to 5.25V)                                                                                                                                          |

|           | CMOS 1.5V*          | CMOS logic input and / or output, 1.5V I/O supply level or tolerance Used for HD Audio. <b>Should</b> be 1.8V signal tolerant.                                                                                     |

|           | CMOS 1.8V           | CMOS logic input and / or output, 1.8V I/O supply level or tolerance. Used for majority of SMARC I/O                                                                                                               |

|           | CMOS 3.3V           | CMOS logic input and / or output, 3.3V I/O supply level or tolerance                                                                                                                                               |

|           | CMOS<br>VDD_JTAG_IO | VDD_JTAG_IO is specific to the Module design. It <i>may</i> be 1.8V, 3.3V, or other value in the 0 to 3.3V range. The JTAG emulator adjusts to the VDD_JTAG_IO level provided by the Module, on the JTAG connector |

|           | GBE MDI             | Differential analog signaling for Gigabit Media Dependent Interface                                                                                                                                                |

|           |                     |                                                                                                                                                                                                                    |

|           | LVDS DP             | LVDS signaling used for DisplayPort devices                                                                                                                                                                        |

|           | LVDS D-PHY          | LVDS signaling used for MIPI CSI camera interfaces                                                                                                                                                                 |

|           | LVDS LCD            | LVDS signaling used for LVDS LCD displays                                                                                                                                                                          |

| -         |                     |                                                                                                                                                                                                                    |

|           | LVDS PCIE           | LVDS signaling used for PCIE interfaces according to the PCI Express specification                                                                                                                                 |

|           | LVDS SATA           | LVDS signaling used for SATA interfaces                                                                                                                                                                            |

|           | TMDS                | LVDS signaling used for HDMI display interfaces                                                                                                                                                                    |

|           | USB                 | DC coupled differential signaling used for traditional (non- Super-Speed) USB signals                                                                                                                              |

|           | USB SS              | LVDS signaling used for Super Speed USB 3.0                                                                                                                                                                        |

|           | USB VBUS 5V         | 5V tolerant input for USB VBUS detection                                                                                                                                                                           |

### 4.2 Internal Display Interfaces

Single channel, dual channel or two single channel LVDS display panel interfaces are defined. The implementation of two single channel LVDS display interfaces is not expected to be common but is defined as an option for Module vendors. The LVDS interfaces support 18 and 24 bit display implementations. Alternatively, the SMARC LVDS pins may also be used to implement eDP or MIPI DSI display interfaces. See Sections 4.2.3 LVDS / eDP Pin Sharing and 4.2.4 LVDS / DSI Pin Sharing below. In a Module implementation with two single LVDS channels, the panel EDID proms would be in conflict and measures need to be taken to avoid this. One possible solution is that the 2<sup>nd</sup> LVDS EDID prom could be read over the I2C\_GP pin pair rather than the I2C\_LCD pin pair.

### 4.2.1 Primary LCD Display Support Signals

The signals in the table below support the LVDS LCD interfaces.

| Signal Name       | Direction    | Type /<br>Tolerance | Description                                                                                                                       |

|-------------------|--------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| LCD[0:1]_VDD_EN   | Output       | CMOS 1.8V           | High enables panel VDD                                                                                                            |

| LCD[0:1]_BKLT_EN  | Output       | CMOS 1.8V           | High enables panel backlight                                                                                                      |

| LCD[0:1]_BKLT_PWM | Output       | CMOS 1.8V           | Display backlight PWM control                                                                                                     |

| I2C_LCD_DAT       | Bi-Dir<br>OD | CMOS 1.8V           | I2C data – to read LCD display EDID EEPROMs Be aware of possible EDID PROM address conflicts if multiple displays are implemented |

| I2C_LCD_CK        | Output       | CMOS 1.8V           | I2C clock – to read LCD display EDID EEPROMs                                                                                      |

### 4.2.2 Primary Display - 18 / 24 Bit LVDS LCD Dual Channel

The Module **should** implement an 18 / 24 bit dual channel LVDS output stream for the Primary display. This stream is usually created from the parallel RGB data, and usually carries the same display information, but in the serialized LVDS format. Control data (HS, VS, DE) are included in the LVDS stream.

| Signal Name                          | Direction | Type /<br>Tolerance | Description                              |

|--------------------------------------|-----------|---------------------|------------------------------------------|

| LVDS[0:1]_[0:3]+<br>LVDS[0:1]_[0:3]- | Output    | LVDS LCD            | LVDS LCD data channel differential pairs |

| LVDS[0:1]_CK+<br>LVDS[0:1]_CK-       | Output    | LVDS LCD            | LVDS LCD differential clock pair         |

All 18 bit TFT panels use the same LVDS color mapping. Only 3 data pairs (LVDS[0:1]\_[0:2] +/-) and the clock pair are needed to drive an 18 bit TFT panel.

Unfortunately, there are two 24 bit LVDS color mappings in the industry:

- Most significant color bits on the 4<sup>th</sup> LVDS data pair (LVDS[0:1]\_[3] +/- here). This is the more common 24 bit mapping. It is not compatible with the 18 bit LVDS color mapping.

- Least significant color bits on the 4<sup>th</sup> LVDS data pair. This is compatible with the 18 LVDS color mapping.

Modules that implement LVDS **shall** implement single channel 18 bit LVDS; **should** implement a 24 bit "18 bit compatible" LVDS mapping and **may** implement the "MS bit on 4<sup>th</sup> LVDS pair" mapping. The second LVDS channel **may** be implemented.

Details on LVDS color mappings are provided in Section 9 Appendix A: LVDS LCD Color Mappings.

# 4.2.3 LVDS / eDP Pin Sharing

Pins used for LVDS LCD support **may** alternatively be used to support up to two Embedded DisplayPorts. The AC coupling required for eDP operation **shall** be done off-Module.

| LVDS Pin Pairs         | LCD Support Pins /<br>Other Pins | eDP Usage              | Notes                                                                      |

|------------------------|----------------------------------|------------------------|----------------------------------------------------------------------------|

| LVDS0_0+<br>LVDS0_0-   |                                  | eDP0_TX0+<br>eDP0_TX0- | eDP0 data pair 0                                                           |

| LVDS0_1+<br>LVDS0_1-   |                                  | eDP0_TX1+<br>eDP0_TX1- | eDP0 data pair 1                                                           |

| LVDS0_2+<br>LVDS0_2-   |                                  | eDP0_TX2+<br>eDP0_TX2- | eDP0 data pair 2                                                           |

| LVDS0_3+<br>LVDS0_3-   |                                  | eDP0_TX3+<br>eDP0_TX3- | eDP0 data pair 3                                                           |

| LVDS0_CK+<br>LVDS0_CK- |                                  | eDP0_AUX+<br>eDP0_AUX- | eDP0 auxiliary channel pair                                                |

| LVDS1_0+<br>LVDS1_0-   |                                  | eDP1_TX0+<br>eDP1_TX0- | eDP1 data pair 0                                                           |

| LVDS1_1+<br>LVDS1_1-   |                                  | eDP1_TX1+<br>eDP1_TX1- | eDP1 data pair 1                                                           |

| LVDS1_2+<br>LVDS1_2-   |                                  | eDP1_TX2+<br>eDP1_TX2- | eDP1 data pair 2                                                           |

| LVDS1_3+<br>LVDS1_3-   |                                  | eDP1_TX3+<br>eDP1_TX3- | eDP1 data pair 3                                                           |

| LVDS1_CK+<br>LVDS1_CK- |                                  | eDP1_AUX+<br>eDP1_AUX- | eDP1 auxiliary channel pair                                                |

|                        | I2C_LCD_CK<br>I2C_LCD_DAT        |                        | Optional - eDP panel information is usually obtained over the eDP AUX pair |

|                        | LCD[0:1]_VDD_EN                  | LCD[0:1]_VDD_EN        | eDP 0/1 VDD_EN support over EDP_AUX channel is preferable                  |

|                        | LCD[0:1]_BKLT_EN                 | LCD[0:1]_BKLT_EN       | eDP 0/1 BKLT_EN support over EDP_AUX channel is preferable                 |

|                        | LCD[0:1]_BKLT_PWM                | LCD[0:1]_BKLT_PWM      | eDP 0/1 BKLT_PWM support over EDP_AUX channel is preferable                |

|                        |                                  | EDP[0:1]_HPD           | eDP 0/1Hot Plug Detect pins                                                |

# 4.2.4 LVDS / DSI Pin Sharing

Pins used for LVDS LCD support *may* alternatively be used to support a MIPI DSI (Display Serial Interface). There is no AC coupling required for DSI operation.

| LVDS Pin Pairs         | LCD Support Pins /<br>Other Pins | DSI Usage              | Notes                         |

|------------------------|----------------------------------|------------------------|-------------------------------|

| LVDS0_0+<br>LVDS0_0-   |                                  | DSI0_D0+<br>DSI0_D0-   | DSI0 data pair 0              |

| LVDS0_1+<br>LVDS0_1-   |                                  | DSI0_D1+<br>DSI0_D1-   | DSI0 data pair 1              |

| LVDS0_2+<br>LVDS0_2-   |                                  | DSI0_D2+<br>DSI0_D2-   | DSI0 data pair 2              |

| LVDS0_3+<br>LVDS0_3-   |                                  | DSI0_D3+<br>DSI0_D3-   | DSI0 data pair 3              |

| LVDS0_CK+<br>LVDS0_CK- |                                  | DSI0_CLK+<br>DSI0_CLK- | DSI0 clock pair               |

| LVDS1_0+<br>LVDS1_0-   |                                  | DSI1_D0+<br>DSI1_D0-   | DSI1 data pair 0              |

| LVDS1_1+<br>LVDS1_1-   |                                  | DSI1_D1+<br>DSI1_D1-   | DSI1 data pair 1              |

| LVDS1_2+<br>LVDS1_2-   |                                  | DSI1_D2+<br>DSI1_D2-   | DSI1 data pair 2              |

| LVDS1_3+<br>LVDS1_3-   |                                  | DSI1_D3+<br>DSI1_D3-   | DSI1 data pair 3              |

| LVDS1_CK+<br>LVDS1_CK- |                                  | DSI1_CLK+<br>DSI1_CLK- | DSI1 clock pair               |

|                        | I2C_LCD_CK<br>I2C_LCD_DAT        |                        |                               |

|                        | LCD[0:1]_VDD_EN                  | LCD[0:1]_VDD_EN        |                               |

|                        | LCD[0:1]_BKLT_EN                 | LCD[0:1]_BKLT_EN       |                               |

|                        | LCD[0:1]_BKLT_PWM                | LCD[0:1]_BKLT_PWM      |                               |

|                        | EDP[0:1]_HPD                     | DSI[0:1]_TE            | DSI 0/1 tearing effect signal |

# 4.2.5 Secondary (HDMI) Display

| Signal Name                  | Direction | Type /<br>Tolerance | Description                         |

|------------------------------|-----------|---------------------|-------------------------------------|

| HDMI_D[0:2]+<br>HDMI_D[0:2]- | Output    | TMDS                | TMDS / HDMI data differential pairs |

| HDMI_CK+<br>HDMI_CK-         | Output    | TMDS                | HDMI differential clock output pair |

| HDMI_HPD                     | Input     | CMOS 1.8V           | HDMI Hot Plug Detect input          |

| HDMI_CTRL_DAT                | Bi-Dir OD | CMOS 1.8V           | I2C data line dedicated to HDMI     |

| HDMI_CTRL_CK                 | Output OD | CMOS 1.8V           | I2C clock line dedicated to HDMI    |

HDMI displays uses 5V I2C signaling. The Module HDMI\_CTRL\_DAT and HDMI\_CTRL\_CK signals need to be level translated on the Carrier from the Module 1.8V level. A similar consideration applies to the HDMI\_HPD signal. There are a number of single chip devices on the market that perform ESD protection and control signal level shifting for HDMI interfaces. The Texas Instruments TPD12S016 is one such device.

### 4.2.6 DP++ Operation Over SMARC HDMI Pins

The SMARC HDMI pins **may** alternatively be used for DisplayPort++ (DP++) operation. This is Module vendor dependent.

| DP++ Use                 | Direction | DP++ Description                                                                                                                                                              | Coupling /<br>Tolerance      | SMARC Signal Name for native HDMI |

|--------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-----------------------------------|

| DP1_LANE0+<br>DP1_LANE0- | Output    | DP Data Pair 0                                                                                                                                                                | AC Coupled <b>off</b> module | HDMI_D2+<br>HDMI_D2-              |

| DP1_LANE1+<br>DP1_LANE1- | Output    | DP Data Pair 1                                                                                                                                                                | AC Coupled <b>off</b> module | HDMI_D1+<br>HDMI_D1-              |

| DP1_LANE2+<br>DP1_LANE2- | Output    | DP Data Pair 2                                                                                                                                                                | AC Coupled <b>off</b> module | HDMI_D0+<br>HDMI_D0-              |

| DP1_LANE3+<br>DP1_LANE3- | Output    | DP Data Pair 3                                                                                                                                                                | AC Coupled <b>off</b> module | HDMI_CK+<br>HDMI_CK-              |

| DP1_HPD                  | Input     | DP Hot Plug Detect input                                                                                                                                                      | DC coupled<br>CMOS 1.8V      | HDMI_HPD                          |

| DP1_AUX-                 | Bi-Dir    | DP AUX Channel<br>(- part of pair)                                                                                                                                            | AC Coupled <b>on</b> module  | HDMI_CTRL_DAT                     |

| DP1_AUX+                 | Bi-Dir    | DP AUX Channel (+ part of pair)                                                                                                                                               | AC Coupled <b>on</b> module  | HDMI_CTRL_CK                      |

| DP1_AUX_SEL              | Input     | Pulled to GND on Carrier for DP operation in Dual Mode (DP++) implementations. Driven to 1.8V on Carrier for HDMI operation. Terminated on Module through 1M resistor to GND. | DC coupled CMOS 1.8V         | n/a                               |

Dual Mode (HDMI and DisplayPort on the same pins) implementations **may** be realized. This is desirable for SOCs that natively implement this capability. With such SOCs, the primary Dual Mode implementation challenge is that the HDMI\_CTRL\_DAT and HDMI\_CTRL\_CK lines are DC coupled, but the DP\_AUX+ /-pair must be AC coupled. A set of FET switches is usually used to sort this out. The FET gates can be controlled by the AUX\_SEL pin function.

### 4.2.7 DP++

A DP++ interface can output signals that are formatted per either DP or HDMI / DVI protocols. The signal levels are DP compliant. For DP use, off-module coupling caps are needed on the 4 DP display data lanes. A Carrier Board level translator is usually needed for HDMI / DVI operation.

DP++ or DisplayPort++ (also named as Dual-mode DisplayPort) can directly output HDMI and DVI signals. The level adaptation can be implemented on the Carrier or via plug in cable adapter. In case of Carrier Board implementation a level shifter adjusts the I/O voltage to HDMI/DVI compliant signal levels. A dual-mode chipset switches to DVI/HDMI mode (4-lane main DisplayPort link and AUX channel) if a DVI or HDMI passive adapter is detected (by DP0\_AUX\_SEL).

| Signal Name                      | Direction | Type /<br>Tolerance | Description                                                                             |

|----------------------------------|-----------|---------------------|-----------------------------------------------------------------------------------------|

| DP0_LANE[0:3]+<br>DP0_LANE[0:3]- | Output    | LVDS PCIE           | Four DisplayPort differential pair lines                                                |

| DP0_AUX+<br>DP0_AUX -            | Bi-Dir    | LVDS PCIE           | Auxiliary channel used for link management and device control. Differential pair lines. |

| DP0_HPD                          | Input     | CMOS 1.8V           | Hot plug detection signal.                                                              |

| DP0_AUX_SEL                      | Input     | CMOS 1.8V           | Pulled to GND on Carrier for DP operation in Dual Mode implementations.                 |

### 4.3 Camera Interfaces

SMARC 2.0 defines two MIPI CSI serial camera interfaces. The defined CSI0 interface supports up to two differential data lanes (CSI0\_D[0:1]+/- signals). CSI1 *may* be implemented with up to four differential data lanes (CSI1\_D[0:3]+/- signals) to support higher resolution cameras.

Both MIPI CSI interfaces support MIPI-CSI 2.0 but are also prepared to support the implementation of MIPI-CSI 3.0. Both standards continue to evolve (see <a href="http://mipi.org/specifications/camera-interface">http://mipi.org/specifications/camera-interface</a>). While MIPI-CSI 2.0 utilizes an I2C bus (I2C\_CAM[0:1]) to communicate with the camera the MIPI-CSI 3.0 uses a differential data lane (CSI[0:1]\_TX+/-).

### 4.3.1 Camera Configurations

| Configuration | CSI0 | CSI1                                |

|---------------|------|-------------------------------------|

| Serial        |      | CSI1 – 2 or 4 lanes<br>MIPI-CSI 2.0 |

| Alternative   |      | CSI1 – 2 or 4 lanes<br>MIPI-CSI 3.0 |

### 4.3.2 Camera Power Enables and Resets

| Signal Name          | Direction | Type /<br>Tolerance | GPIO Use | Sanctioned Alternate Uses                 |

|----------------------|-----------|---------------------|----------|-------------------------------------------|

| GPIO0 /<br>CAM0_PWR# | Bi-Dir    | CMOS 1.8V           | GPIO0    | Camera 0 Power Enable, active low output. |

| GPIO1 /<br>CAM1_PWR# | Bi-Dir    | CMOS 1.8V           | GPIO1    | Camera 1 Power Enable, active low output  |

| GPIO2 /<br>CAM0_RST# | Bi-Dir    | CMOS 1.8V           | GPIO2    | Camera 0 Reset, active low output         |

| GPIO3 /<br>CAM1_RST# | Bi-Dir    | CMOS 1.8V           | GPIO3    | Camera 1 Reset, active low output         |

### 4.3.3 Camera I2C Support

The I2C\_CAM\_ port is intended to support serial cameras. Most contemporary cameras with I2C support allow a choice of two I2C address ranges.

| Signal Name      | Direction | Type / Tolerance | Description                                                                                                  |

|------------------|-----------|------------------|--------------------------------------------------------------------------------------------------------------|

| I2C_CAM[0:1]_DAT | Bi-Dir OD | CMOS 1.8V        | I2C data: Serial camera support link for serial cameras Alternative function: CSI[0:1]_TX- for MIPI CSI 3.0  |

| I2C_CAM[0:1]_CK  | Bi-Dir OD | CMOS 1.8V        | I2C clock: Serial camera support link for serial cameras Alternative function: CSI[0:1]_TX+ for MIPI CSI 3.0 |

# 4.3.4 MIPI CSI Configuration CSI-2 and CSI-3

The newer version of the MIPI Camera Serial Interface CSI-3 no longer uses an I2C bus to transmit commands an configurations to the camera. A newly defined high speed differential signal pair is used instead.

| Signal Name                  | Direction | Type /<br>Tolerance | Description                                            |

|------------------------------|-----------|---------------------|--------------------------------------------------------|

| CSI[0:1]_TX+<br>CSI[0:1]_TX- | Output    | TMDS                | Differential data pairs used for camera configurations |

### 4.3.5 Serial Cameras In

Two MIPI CSI camera interfaces are supported. The CSI0 interface supports two lanes, the CSI1 interface supports 4 lanes. MIPI CSI 2.0 and MIPI CSI 3.0 are supported.

| Signal Name                                                  | Direction | Type / Tolerance | Description                                                                             |

|--------------------------------------------------------------|-----------|------------------|-----------------------------------------------------------------------------------------|

| CSI0_D[0:1]+<br>CSI0_D[0:1]-<br>CSI1_D[0:3]+<br>CSI1_D[0:3]- | Input     | LVDS D-PHY       | CSI differential data inputs                                                            |

| CSI[0:1]_CK+<br>CSI[0:1]_CK-                                 | Input     | LVDS D-PHY       | CSI differential clock inputs                                                           |

| CAM_MCK                                                      | Output    | CMOS 1.8V        | Master clock output for CSI camera support ( <i>may</i> be used for CSI0 and / or CSI1) |

| I2C_CAM[0:1]_CK                                              | Bi-Dir OD | CMOS 1.8V        | Alternative use: MIPI-CSI 3.0 configuration CSI[0:1]_TX+                                |

| I2C_CAM[0:1]_DAT                                             | Bi-Dir OD | CMOS 1.8V        | Alternative use: MIPI-CSI 3.0 configuration CSI[0:1]_TX-                                |

# 4.4 SDIO Card (4 bit) Interface

The Carrier SDIO Card may be selected as the Boot Device – see Section 4.17 Boot Select.

| Signal Name | Direction | Type /<br>Tolerance | Description          |

|-------------|-----------|---------------------|----------------------|

| SDIO_D[0:3] | Bi-Dir    | CMOS 3.3V           | 4 bit data path      |

| SDIO_CMD    | Bi-Dir    | CMOS 3.3V           | Command line         |

| SDIO_CK     | Output    | CMOS 3.3V           | Clock                |

| SDIO_WP     | Input     | CMOS 3.3V           | Write Protect        |

| SDIO_CD#    | Input     | CMOS 3.3V           | Card Detect          |

| SDIO_PWR_EN | Output    | CMOS 3.3V           | SD card power enable |

**Note:** There are SD Cards with a 1.8V I/O voltage (UHS-I). SDIO controllers supporting these cards will adjust the I/O voltage levels.

### 4.5 SPI Interfaces

### 4.5.1 SPI0

The Carrier SPI0 device may be selected as the Boot Device – see Section 4.17 Boot Select.

| Signal Name | Direction | Type / Tolerance | Description                                                            |

|-------------|-----------|------------------|------------------------------------------------------------------------|

| SPI0_CS0#   | Output    | CMOS 1.8V        | SPI0 Master Chip Select 0 output Use to select Carrier SPI boot device |

| SPI0_CS1#   | Output    | CMOS 1.8V        | SPI0 Master Chip Select 1 output                                       |

| SPI0_CK     | Output    | CMOS 1.8V        | SPI0 Master Clock output                                               |

| SPI0_DIN    | Input     | CMOS 1.8V        | SPI0 Master Data input (input to CPU, output from SPI device)          |

| SPI0_DO     | Output    | CMOS 1.8V        | SPI0 Master Data output (output from CPU, input to SPI device)         |

### 4.5.2 eSPI/SPI1

| Signal Name      | Direction | Type / Tolerance | Description                                                                                                                                                                                                                                                                       |

|------------------|-----------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ESPI_CK          | Output    | CMOS 1.8V        | ESPI Master Clock Output This pin provides the reference timing for all the serial input and output operations.                                                                                                                                                                   |

| ESPI_CS[0:1]#    | Output    | CMOS 1.8V        | ESPI Master Chip Select Outputs Driving Chip Select# low selects a particular eSPI slave for the transaction. Each of the eSPI slaves is connected to a dedicated Chip Select# pin.                                                                                               |

| ESPI_IO_[0:3]    | Bi-Dir    | CMOS 1.8V        | ESPI Master Data Input / Outputs These are bi-directional input/output pins used to transfer data between master and slaves. In Single I/O mode, ESPI_IO_0 is the eSPI master output/eSPI slave input (MOSI) whereas ESPI_IO_1 is the eSPI master input/eSPI slave output (MISO). |

| ESPI_RESET#      | Output    | CMOS 1.8V        | ESPI Reset Reset the eSPI interface for both master and slaves. eSPI Reset# is typically driven from eSPI master to eSPI slaves.                                                                                                                                                  |

| ESPI_ALERT[0:1]# | Input     | CMOS 1.8V        | This pin is used by eSPI slave to request service from eSPI master.  Alert# is an open-drain output from the slave. This pin is optional for Single Master-Single Slave configuration where I/O[1] can be used to signal the Alert event.                                         |

### 4.6 Audio

Two audio interfaces are defined. One is pin shared with HDA, I2S1 from SMARC V1.1 has been deprecated.

The I2S interface is typically used for ARM processor implementation. HDA is typically used for x86 processor implementations. The HDA interface can also be used for a second I2S interface.

### 4.6.1 I2S

Two I2S interfaces are defined. These are typically used for digital audio I/O and other modest bandwidth functions. A common audio master clock signal is also defined.

| Signal Name | Direction | Type / Tolerance | Description                             |

|-------------|-----------|------------------|-----------------------------------------|

| I2S0_LRCK   | Bi-Dir    | CMOS 1.8V        | Left& Right audio synchronization clock |

| I2S0_SDOUT  | Output    | CMOS 1.8V        | Digital audio Output                    |

| I2S0_SDIN   | Input     | CMOS 1.8V        | Digital audio Input                     |

| I2S0_CK     | Bi-Dir    | CMOS 1.8V        | Digital audio clock                     |

| AUDIO_MCK   | Output    | CMOS 1.8V        | Master clock output to Audio codecs     |

### 4.6.2 HDA / I2S

| Signal Name | Direction | Type / Tolerance     | Description                                                                           |

|-------------|-----------|----------------------|---------------------------------------------------------------------------------------|

| HDA_SYNC    | Bi-Dir    | CMOS 1.5V /<br>1.8V* | Left& Right audio synchronization clock / HDA sync<br>Alternative use: I2S2_LRCK      |

| HDA_SDO     | Output    | CMOS 1.5V /<br>1.8V* | I2S Digital audio Output / High Definition Audio data out Alternative use: I2S2_SDOUT |

| HDA_SDI     | Input     | CMOS 1.5V /<br>1.8V* | I2S Digital audio Input / High Definition Audio data in Alternative use: I2S2_SDI     |

| HDA_CK      | Bi-Dir    | CMOS 1.5V /<br>1.8V* | I2S Digital audio clock/ High Definition Audio clock<br>Alternative use: I2S2_CK      |

| HDA_RST#    | Output    | CMOS 1.5V /<br>1.8V* | HDA reset output (by means of GPIO4)                                                  |

**Note:** The numbering of the secondary, alternative I2S interface is #2 because the I2S interface #1 from SMARC 1.1 was removed for SMARC 2.0.

Per the HD Audio specification, HD Audio *may* be run at either 1.5V or 3.3V. SMARC requires 1.5V or 1.8V HD Audio signaling. Please check with your module vendor if 1.5V or 1.8V are supported and use an audio codec that is capable to support the regarding I/O voltage. The SMARC HD Audio pins are shared with the I2S2 pins, which are defined to be 1.8V. This specification ignores the discrepancy between the 1.5V and 1.8V signaling, as the chance of damage in mismatched systems is negligible. ARM SOCs generally run I2S audio and will likely use 1.8V signaling. X86 SOCs generally run 1.5V signal levels on the HD Audio interface.

### 4.7 I2C Interfaces

The Module supports six I2C interfaces, per the following table. Except for the LCD and HDMI Module I2C interfaces, the I2C ports **should** be multi-master capable. Data rates of 100 kHz and 400 kHz **should** be supported.

| I2C Port             | Primary Purpose          | Alternate Use                   | I/O Voltage<br>Level |

|----------------------|--------------------------|---------------------------------|----------------------|

| I2C_PM               | Power Management support | System configuration management | CMOS 1.8V            |

| I2C_CAM0<br>I2C_CAM1 | Camera support           | General Purpose                 | CMOS 1.8V            |

| I2C_GP               | General purpose use      |                                 | CMOS 1.8V            |

| I2C_LCD              | LCD display support      | General Purpose                 | CMOS 1.8V            |

| HDMI_CTRL            | HDMI control             |                                 | CMOS 1.8V            |

All I2C interfaces but the I2C\_GP interface are described in the section served by that I2C link (LCD, HDMI, Camera Interface, etc). The I2C\_GP Module interface consists of the following two pins:

| Signal Name | Direction | Type / Tolerance | Description                      |

|-------------|-----------|------------------|----------------------------------|

| I2C_GP_CK   | Bi-Dir OD | CMOS 1.8V        | I2C General Purpose clock signal |

| I2C_GP_DAT  | Bi-Dir OD | CMOS 1.8V        | I2C General Purpose data signal  |

# 4.8 Asynchronous Serial Ports

Module pins for up to four asynchronous serial ports are defined. The ports are designated SER0 – SER3. Ports SER0 and SER2 are 4 wire ports (2 data lines and 2 handshake lines). Ports SER1 and SER3 are 2 wire ports (data only).

| Signal Name | Direction | Type / Tolerance | Description                             |

|-------------|-----------|------------------|-----------------------------------------|

| SER[0:3]_TX | Output    | CMOS 1.8V        | Asynchronous serial port data out       |

| SER[0:3]_RX | Input     | CMOS 1.8V        | Asynchronous serial port data in        |

| SER[0]_RTS# | Output    | CMOS 1.8V        | Request to Send handshake line for SER0 |

| SER[0]_CTS# | Input     | CMOS 1.8V        | Clear to Send handshake line for SER0   |

| SER[2]_RTS# | Output    | CMOS 1.8V        | Request to Send handshake line for SER2 |

| SER[2]_CTS# | Input     | CMOS 1.8V        | Clear to Send handshake line for SER2   |

### 4.9 CAN Bus

| Signal Name | Direction | Type / Tolerance | Description         |

|-------------|-----------|------------------|---------------------|

| CAN[0:1]_TX | Output    | CMOS 1.8V        | CAN Transmit output |

| CAN[0:1]_RX | Input     | CMOS 1.8V        | CAN Receive input   |

### 4.10 USB Interfaces

SMARC 2.0 provides six sets of USB 2.0 signals and two sets of USB 3.0 Super Speed signals. USB OTG and USB Client functionalities are also supported.

USB 3.0 is supported for the USB ports 2 and 3. For implementation of USB 3.0 OTG or USB 3.0 host USB3 *may* be used.

The USB0 port **shall** be available as a USB 2.0 client. It **may** also be available as an OTG port (and, by extension, as a host), or as a host (some SOCs allow a USB port to be configured as client or host, but do not support full OTG functionality).

### 4.10.1 USB Signal Assignments

|      | USB 2.0 | USB 3.0 | OTG/VBUS | Client<br>Capability |

|------|---------|---------|----------|----------------------|

| USB0 | х       |         | х        | х                    |

| USB1 | х       |         |          |                      |

| USB2 | х       | х       |          |                      |

| USB3 | х       | х       | х        | х                    |

| USB4 | х       |         |          |                      |

| USB5 | х       |         |          |                      |

# 4.10.2 USB Signals

| Signal Name                    | Direction | Type / Tolerance | Description                                                                                                                                                                                                                                                                                                                                                                           |

|--------------------------------|-----------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| USB[0:5]+<br>USB[0:5]-         | Bi-Dir    | USB              | Differential USB 2.0 data pairs                                                                                                                                                                                                                                                                                                                                                       |

| USB[0:5]_EN_OC#                | Bi-Dir OD | CMOS 3.3V        | Pulled low by Module OD driver to disable USB0 power. Pulled low by Carrier OD driver to indicate over-current situation. A pull-up <i>shall</i> be present on the Module to a 3.3V rail. The pull-up rail <i>may</i> be switched off to conserve power if the USB port is not in use. Further details <i>may</i> be found in Section <i>4.10.3 USB[0:5]_EN_OC#</i> Discussion below. |

| USB0_VBUS_DET<br>USB3_VBUS_DET | Input     | USB VBUS 5V      | USB host power detection, when this port is used as a device.                                                                                                                                                                                                                                                                                                                         |

| USB0_OTG_ID<br>USB3_OTG_ID     | Input     | CMOS 3.3V        | USB OTG ID input, active high.                                                                                                                                                                                                                                                                                                                                                        |

| USB[2:3]SSRX-<br>USB[2:3]SSRX+ | Input     | USB SS           | Receive signal differential pairs for SuperSpeed USB data Coupling caps for RX pairs are <i>off</i> -Module                                                                                                                                                                                                                                                                           |

| USB[2:3]SSTX-<br>USB[2:3]SSTX+ | Output    | USB SS           | Transmit signal differential pairs for SuperSpeed USB data Coupling caps for RX pairs are <i>off</i> -Module                                                                                                                                                                                                                                                                          |

### 4.10.3 USB[0:5]\_EN\_OC# Discussion

The Module USB[0:5]\_EN\_OC# pins are multi-function Module pins, with a pull-up to a 3.3V rail on the Module, an OD driver on the Module, and, if the OC# (over-current) monitoring function is implemented on the Carrier, an OD driver on the Carrier. The use is as follows:

- 1) On the Carrier board, for external plug-in USB peripherals (USB memory sticks, cameras, keyboards, mice, etc.) USB power distribution is typically handled by USB power switches such as the Texas Instruments TPS2052B or the Micrel MIC2026-1 or similar devices. The Carrier implementation is more straightforward if the Carrier USB power switches have active—high power enables and active low open drain OC# outputs (as the TI and Micrel devices referenced do). The USB power switch Enable and OC# pins for a given USB channel are tied together on the Carrier. The USB power switch enable pin must function with a low input current. The TI and Micrel devices referenced above require 1 microampere or less, at a 3.3V enable voltage level.

- 2) The Module drives USB[0:5]\_EN\_OC# low to disable the power delivery to the USB[0:5] device.

- 3) The Module floats USB[0:5]\_EN\_OC# to enable power delivery. The line is pulled to 3.3V by the Module pull-up, enabling the Carrier board USB power switch. If there is a USB over-current condition, the Carrier board USB power switch drives the USB[0:5]\_EN\_OC# line low. This removes the over-current condition (by disabling the USB switch enable input), and allows Module software to detect the over-current condition. The Module software **should** look for a falling edge interrupt on USB[0:5]\_EN\_OC#, while the port is enabled, to detect the OC# condition. The OC# condition will not last long, as the USB power switch is disabled when the switch IC detects the OC# condition. If the USB power to the port is disabled (USB[0:5]\_EN\_OC# is driven low by the Module) then the Module software must be aware that the port is disabled, and the low input value on the port does not indicate an over-current condition (because the port power is disabled). If the USB power to the port is disabled, then the Module **may** remove the 3.3V pull-up voltage to the USB[0:5]\_EN\_OC# node, to save the current drain through the pull-up resistor. This is optional and Module design dependent.